# Impact of Strain on Fully Depleted Strained Gate Stack Double Gate MOSFET: A Simulation Study

K. P. Pradhan\*1, S. K. Mohapatra\*2, P. K Sahu\*3, and S. Parija\*4, Non-members

## ABSTRACT

The fusion of strain engineering and multigate technology is implemented to design an advanced MOSFET model i.e. Fully Depleted Strained Gate Stack Double Gate (FD-S-GS-DG) in nanoscale regime. Both DC and Analog performances of FD-S-GS-DG are analyzed by varying the Ge mole fraction (X). The sensitivity of crucial device parameters like threshold voltage  $(V_{th})$ , subthreshold swing (SS), on-current  $(I_{on})$ , off state leakage current  $(I_{off})$ , onoff ratio  $(I_{on}/I_{off})$ , transconductance  $(g_m)$ , output conductance  $(g_d)$ , early voltage  $(V_{EA})$ , gain  $(A_V)$ , transconductance generation factor (TGF) towards X are successfully evaluated and presented. From the obtained results by choosing appropriate value of X, we can significantly enhance the device performance.

**Keywords**: Gate stack (GS), Strain, Ge mole fraction (X), SCEs, Analog performance.

# 1. INTRODUCTION

The central component of semiconductor electronics is the integrated circuit (IC), which combines the basic elements of electronic circuits - such as transistors, diodes, capacitors, resistors and inductors on one semiconductor substrate. The two most important elements of silicon electronics are transistors and memory devices. For logic applications generally MOSFETs (Metal Oxide Semiconductor Field Effect Transistor) are used [1]-[4].

The semiconductor industry has showcased a spectacular exponential growth in the number of transistors per integrated circuit for several decades, as predicted by Moore's law [2]. The future technology trend predicted by ITRS (International Technology Roadmap for Semiconductors) [4], physical dimensions and electrostatic limitations faced by conventional process and fabrication technologies will require the dimensional scaling of complementary metal-oxide-semiconductor (CMOS) devices

within the next decade [5], [6]. To enable future technology scaling, new device structures for next-generation technology have been proposed. Some of the new technologies are Silicon On Insulator (SOI) [7], Strained Silicon (S-Si) at the channel [8]-[10], inclusion of high-k dielectric materials in gate oxide [11]-[13] and Multi gate MOSFETs [14]-[16]. Many of these devices have been shown to have favorable device properties and new device characteristics, and require new fabrication techniques. These nanoscale devices have significant potential to revolutionize the fabrication and integration of electronic systems and scale beyond the perceived scaling limitations of traditional CMOS.

The salient objectives of this work is to design and simulate one optimum device i.e. Fully Depleted Strained Gate Stack DG (FD-S-GS-DG) MOSFET with optimized device parameters and analyze the sensitivity of important device performances including static and analog towards Ge mole fraction content (X) for both low power and high frequency applications.

## 2. DEVICE DESIGN AND SIMULATION

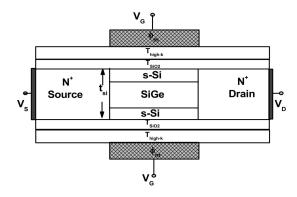

The schematic structure of FD-S-GS-DG MOS-FET is shown in Fig. 1. In this structure the channel length (L) and Source/Drain length  $(L_S/L_D)$  is fixed as 40nm, the silicon thickness  $(t_{Si})$  as 10nm and a uniform density of  $N_D$  as  $10^{20}$  cm<sup>-3</sup> is taken. The channel is doped with  $(N_A) = 10^{16} \ cm^{-3}$ . Gate stack configuration is designed by considering  $SiO_2$  layer thickness is fixed at 0.6nm and above this layer 0.5nm equivalent thickness of high-k layer,  $HfO_2$  (k=24) is deposited, so that the EOT reaches 1.1nm. The work function of the gate material (Molybdenum) is considered at 4.6 eV. The Ge composition (X) in the layer SiGe is varied from 0 to 0.4 [17]-[19]. The strained silicon can be formed by following the steps: (i) epitaxial growth of SiGe layer on Si substrate (ii) ion implantation and high temperature annealing (iii) removal of surface layer and regrowth of Si/SiGe layer [20].

In the simulation, the inversion-layer Lombardi constant voltage and temperature (CVT) mobility model has been used. The Shockley-Read-Hall (SRH) generation and recombination parameters simulate the leakage currents. The model Fermi-Dirac uses a Rational Chebyshev approximation that gives results

Manuscript received on June 06, 2015 ; revised on June 11, 2015.

<sup>\*</sup>The authors are with Department of Electrical Engineering, National Institute of Technology (NIT), Rourkela, 769008, Odisha India, E-mail: kp2.etc@gmail.com^1, skmctc74@gmail.com^2, pksahu@nitrkl.ac.in^3, and smita.parija@gmail.com^4.

Fig.1: Schematic structure of FD-S-GS-Double Gate N-MOSFET.

close to the exact values. The Auger recombination models for minority carrier recombination have been used [21].

### 3. RESULTS AND DISCUSSION

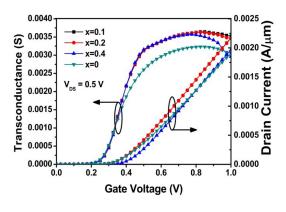

Fig. 2(a) shows the variation of drain current  $(I_D)$  and transconductance  $(g_m)$  with respect to gate voltage  $(V_{GS})$  for various Ge concentrations (X). From the figure, as the Ge concentration is increased, drain current and transconductance is also increased because of the enhancement of carrier mobility caused by the strained silicon due to the lowering of in-plane effective mass and a reduction in intervalley scattering [22]. The output characteristic  $(I_D - V_{DS})$  and output conductance  $(g_d)$  as a function of drain bias  $(V_{DS})$  is plotted in Fig. 2(b). Here also, both the current and output conductance is more for strained silicon as compare to unstrained (X = 0) silicon due to the same mobility effect.

The simulated results for threshold voltage  $(V_{th})$ , subthreshold swing (SS), maximum value of on current  $(I_{on} \text{ (max)})$ , off current  $(I_{off})$ , on-off ratio  $(I_{on}/I_{off})$  are tabulated in Table 1. By comparing those values with Ge concentration (X) varying from 0 (unstrained) to 0.2 (strained), Ion is raised up to 13.4%, and  $I_{on}/I_{off}$  is improved by 1.75% with little compromise in  $I_{off}$ . The SS value increases as X value increases and reaches its maximum for X=0.4.

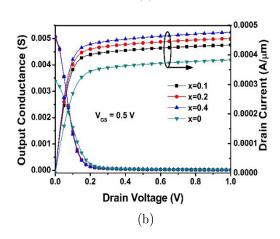

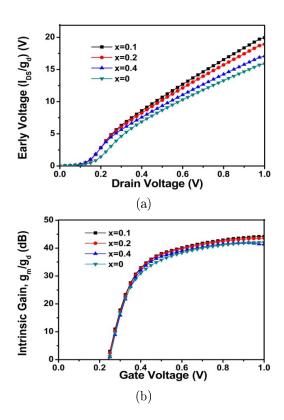

Fig. 3(a) shows the variation of the Early voltage  $(V_{EA})$  with drain bias for various Ge mole fractions (X) at a gate voltage of 0.5 V. The  $V_{EA}$  is more for strained silicon as compare to unstrained silicon. It depicts highest value for X=0.1 and starts decreasing as x value increases. The intrinsic gain  $(A_V)$  of the device, which is a ratio of transconductance and output conductance for various Ge concentrations is plotted against gate voltage  $(V_{GS})$  for  $V_{DS}=0.5$  V is shown in Fig. 3(b). The intrinsic gain  $g_m/g_{ds}$  is a valuable figure of merit for operational transconductance amplifier. Similarly, from the figure, the gain is high for strained silicon from its counterpart unstrained silicon and reaches its maximum value for

(a)

Fig.2: (a) Drain current  $(I_D)$  and transconductance  $(g_m)$  variation with Gate voltage  $(V_{GS})$  for different Ge concentration (X) (b) Drain current  $(I_{DS})$  and output conductance  $(g_d)$  as a function of Drain voltage  $(V_{DS})$  for different Ge concentration (X).

X=0.1. It then starts decreasing as X value increases.

All the extracted values for analog performance are tabulated in Table 2. Similarly, as Ge concentration (X) varies from 0 (unstrained) to 0.2 (strained), transconductance  $(g_m)$  of the device increases by 12.40%, output conductance  $(g_d)$  is increased by 49.31%, early voltage  $(V_{EA})$  is raised by 19.21%, gain of the device is increased by 3.6% and TGF is raised by 9.36%.

# 4. CONCLUSIONS

In this work, one optimum device, i.e. fully depleted strained gate stack double gate (FD-S-GS-DG) MOSFET is designed and simulated to study some aspect of its performance. Both DC and Analog performances are studied by varying the Ge mole fraction (X). The increase in strain, i.e., equivalent Ge content, enhances the performance of FD-S-GS-MOSFET in terms of electrostatic parameters as well in analog parameters because of an increase in the

|                        | _            |                                  |                        | -                          |                       |

|------------------------|--------------|----------------------------------|------------------------|----------------------------|-----------------------|

| Ge Concentration $(X)$ | $V_{th}$ (V) | $SS \pmod{\mathrm{(mV/decade)}}$ | $I_{on} (max) $ $(mA)$ | $I_{off}$ (A)              | $I_{on}/I_{off}$      |

| X=0                    | 0.219        | 62.5057                          | 1.910                  | $3.05\mathrm{E}\text{-}10$ | 6.26E + 09            |

| X = 0.1                | 0.213        | 62.6723                          | 2.116                  | 3.19E-10                   | 6.12E + 09            |

| X = 0.2                | 0.208        | 62.8793                          | 2.166                  | 3.40 E-10                  | 6.37E + 09            |

| X = 0.4                | 0.202        | 63.2893                          | 2.173                  | $3.46\mathrm{E}\text{-}10$ | $6.28\mathrm{E}{+09}$ |

Table 1: Electrostatic parameters for different values of Ge Concentration.

Table 2: Analog parameters for different values of of Ge Concentration.

| Ge concentration $(X)$ | $g_m \text{ (max) (mA)}$ | $g_d (max) (mA)$ | $V_{EA}$ (V) | Gain (dB) | TGF $(V^{-1})$ |

|------------------------|--------------------------|------------------|--------------|-----------|----------------|

| X=0                    | 3.232                    | 3.380            | 15.882       | 42.046    | 39.62          |

| X = 0.1                | 3.572                    | 5.026            | 19.947       | 41.344    | 40.87          |

| X=0.2                  | 3.633                    | 5.047            | 18.933       | 43.599    | 41.98          |

| X = 0.4                | 3.649                    | 5.097            | 17.081       | 44.194    | 42.08          |

Fig.3: (a) Early voltage  $(V_{EA})$  variation with Drain voltage  $(V_{DS})$  for different Ge concentration (X). (b) Intrinsic gain  $(A_V)$  as a function of Gate voltage  $(V_{GS})$  for different Ge concentration (X).

carrier mobility. Never the less, availability of few challenges are trivial even if a long list of advantages exist. According to our demonstrated results, there are undesirable side effects after certain amount of equivalent Ge content (i.e. X=0.4) such as an increase in SS value and a decrease in  $I_{on}$ ,  $g_m$ ,  $V_{EA}$  and gain  $(A_v)$  which may affect the device characteristics and performance significantly. Therefore, we conclude that strained silicon up to some extent of Ge mole fraction shows better results in device performances.

### References

- [1] N. K. Jha, and D. Chen, Nanoelectronic Circuit Design. Springer Science & Business Media, 2010.

- [2] G. E. Moore, and others, "Cramming more components onto integrated circuits," *Proc. IEEE*, vol. 86, no. 1, pp. 82-85, Jan. 1998.

- [3] Y. L. Sung-Mo Kang, Cmos Digital Integrated Circuits. Tata McGraw-Hill Education, 2003, p. 655.

- [4] "The International Technology Roadmap for Semiconductors," 2011.

- [5] C. Hu, Modern Semiconductor Devices for Integrated Circuits. Prentice Hall, 2009.

- [6] J. P. Colinge, "The new generation of SOI MOS-FETs," Rom. J. Inf. Sci. Technol., vol. 11, no. 1, pp. 3-15, Jan. 2008.

- [7] M. Bruel, "Silicon on insulator material technology," *Electron. Lett.*, vol. 31, no. 14, pp. 1201-1202, Jul. 1995.

- [8] T. A. Langdo, M. T. Currie, R. Hammond, A. J. Lochtefeld, and E. A. Fitzgerald, "Strainedsemiconductor-on-insulator device structures." Google Patents, 2006.

- [9] S. K. Mohapatra, K. P. Pradhan, and P. K. Sahu, "Nanoscale SOI N-MOSFETs with different Gate Engineering having Biaxial Strained Channel - A Superlative Study," J. Electron Devices, vol. 15, pp. 1261-1268, Sep. 2012.

- [10] P. K. Sahu, K. P. Pradhan, S. K. Mohapatra, P. K. Sahu, K. P. Pradhan, and S. K. Mohapatra, "A Study on SCEs of FD-S-SOI MOSFET in Nanoscale," *Univers. J. Electr. Electron. Eng.*, vol. 2, no. 1, pp. 37-43, Jan. 2014.

- [11] C. S. Kim, S. J. Jo, S. W. Lee, W. J. Kim, H. K. Baik, S. J. Lee, D. K. Hwang, and S. Im, "High-k and low-k nanocomposite gate dielectrics for low voltage organic thin film transistors," Appl. Phys. Lett., vol. 88, no. 24, p. 243515, Jun. 2007.

- [12] K. P. Pradhan, S. K. Mohapatra, P. K. Sahu, and D. K. Behera, "Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-

- MOSFET," Microelectronics J., vol. 45, no. 2, pp. 144-151, Feb. 2014.

- [13] P. K. Agarwal, K. P. Pradhan, S. K. Mohapatra, and P. K. Sahu, "Insulating layer parameters are still in reduction of kink," 2012 Nirma Univ. Int. Conf. Eng., 2012, pp. 1-4.

- [14] J. P. Colinge, "The SOI MOSFET: From single gate to multigate," in FinFETs and Other Multi-Gate Transistors, Springer US, 2008, pp. 1âĂŞ48.

- [15] S. K. Mohapatra, K. P. Pradhan, and P. K. Sahu, "Effect of channel and gate engineering on Double Gate (DG) MOSFET-A comparative study," in Emerging Electronics (ICEE), 2012 International Conference on, 2012, pp. 1-3.

- [16] K. P. Pradhan, S. K. Mohapatra, P. K. Agarwal, P. K. Sahu, D. K. Behera, and J. Mishra, "Symmetric DG-MOSFET With Gate and Channel EngineeringâĂŕ: A 2-D Simulation Study," *Microelectron. Solid State Electron*, vol. 2, no. 1, pp. 1-9, Feb. 2013.

- [17] L. Jin, L. Hong-Xia, L. Bin, C. Lei, and Y. Bo, "Study on two-dimensional analytical models for symmetrical gate stack dual gate strained silicon MOSFETs," *Chinese Phys. B*, vol. 19, no. 10, pp. 107302, Oct. 2010.

- [18] K. Kim and T. Won, "Quantum-mechanical modeling and simulation of a novel nano-scale FET: Center-channel (CC) double-gate (DG) MOSFET", J. Korean Phys. Soc., vol. 47, pp. S558-S563, Nov. 2005.

- [19] L. Jin, L. Hongxia, Y. Bo, C. Lei, and L. Bin "A two-dimensional analytical model of fully depleted asymmetrical dual material gate doublegate strained-Si MOSFETs," J. Semicond., vol. 32, no. 4, pp. 44005, Apr. 2011.

- [20] N. Sugiyamaa, T. Mizuno, S. Takagi, M. Koike, and A. Kurob, "Formation of strained-silicon layer on thin relaxed-SiGe/SiO2/Si structure using SIMOX technology," *Thin Solid Films*, 1995, vol. 369, pp. 199-202, 2000.

- [21] http://www.synopsys.com/, "Sentaurus TCAD UserâĂŹs Manual," in Synopsys Sentaurus Device, pp. 191-403.

- [22] J. Welser, J. L. Hoyt, and J. F. Gibbons, "Electron Mobility Enhancement in S trained-Si N-Type Metal-Oxide- Semiconductor Field-Effect Transistors," *IEEE Electron Device Letters*, vol. 15, no. 3, pp. 100-102, Mar. 1994.

Kumar Prasannajit Pradhan completed M.Tech (Res) degree in Nanoelectronic Devices, Electrical Engineering Department from National Institute of Technology (NIT), Rourkela, Odisha, India, in 2013, where he is currently working towards the Ph.D. degree in Nanoelectronics. His current research interests are in the area of modeling and simulation of Silicon on Insulator, Underlap Multigate MOSFETs, FinFETs,

etc. He has authored more than 30 research articles in refereed journals and international conferences. He is a student member of IEEE.

Sushanta Mohapatra received the M.E. degree in Communication Control & Networking from the M.I.T.S, Gwalior, India, in 2001. He is currently pursuing Ph.D. in Department of Electrical Engineering at National Institute of Technology (NIT), Rourkela, India. His research interests include modeling and simulation of nanoscale semiconducting devices and its applications. He has authored 35 papers in various In-

ternational Journals and Conferences. He is a life member of ISTE, IETE and student member of IEEE.

Prasanna Sahu received B.Sc Engineering (El&TCE), M.Sc Engineering (ESC) from Sambalpur University, Odisha, India, and received his Ph.D. degree from Jadavpur University, Kolkata, India, in the year 2008. Currently, he is Associate Professor in Department of Electrical Engineering at National Institute of Technology, Rourkela, Odisha, India. His research interest includes Micro and Nano Electrical Engineering at National Institute of Technology, Rourkela, Odisha, India. His research interest includes Micro and Nano Electrical Engineering at Nano Electr

tronic Devices, VLSI, Communication System. He is also a member of IEEE, and life member of IE, ISTE etc.

Smita Parija completed M.Tech degree in Electronic Systems & Communication, Electrical Engineering Department from National Institute of Technology (NIT), Rourkela, Odisha, India, in 2006, where he is currently working towards the Ph.D. degree in Mobile Communication. His current research interests are in the area of Neural Network, Wireless Communication, Soft Computing, Mobile Communication etc. He is a

student member of IEEE.