# Analytical Approach and Simulation of GaN Single Gate TFET and Gate All around TFET

$T.S.Arun\ Samuel^{*1}$ ,  $N.\ Arumugam^{*2}$ , and  $S.Theodore\ Chandra^{**3}$ , Non-members

## ABSTRACT

In this work, we investigate the impact of Gallium Nitride (GaN) based Single Gate Tunnel field effect transistors (SG TFET) and Gate All Around (GAA) TFET by using analytical models. The models are derived by solving the 2D-Poisson's equation and Parabolic Approximation Technique. The analytical model includes the calculation of the surface potential, lateral electric field and vertical electric field. Finally the drain current is extracted by using Kane's model. The device simulations are carried out using 2-D device simulator, Technology Computer Aided Design (TCAD). The model can be used to study the impact of GaN based SG TFET and GAA TFET in terms of higher ON current characteristics. The results expected by the model are compared with those obtained by 2-D simulation to verify the accuracy of the proposed analytical model.

**Keywords**: Single Gate Tunnel Field Effect Transistor, Gate All around (GAA) TFET, 2D-Poisson's equation, Kane's model, TCAD.

#### 1. INTRODUCTION

Silicon CMOS has been the technology of choice of the micro and nano-electronics industry for the past four decades. In this regard, Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) have become the fundamental building blocks of Very Large Scale Integrated circuits (VLSI) due to their excellent properties. The demand for higher integration density, low power consumption, high speed and low cost requires aggressive scaling of the MOSFETs. While scaling the device, the key factors that limit the performance of MOS devices are increased short channel effects (SCE) and very high leakage current.

In the recent years, Tunnel field effect transistors has been proposed to overcome the short channel effects and reduced leakage current (femto Amps). Apart from merits, TFETs suffer from a low ONcurrent (ION). Therefore various techniques to improve the ION in the TFET has been reported [1-6].

In our previous work, we have presented Dual Material Gate (DMG) TEFT [7], Dual Material Gate TFET [8] and Surrounding Gate TFET [9] in order to improve the ON current characteristics. Eng-Hua [10] proposed germanium TFETs are studied for high performance and low power logic applications using two dimensional device simulations. It has been proved that Ge based TFET could achieve higher ION than Silicon TFET. However in the above structures, the ION current still need to be improved.

This paper deliberates the two promising new directions for tunneling junction formation that alter the ION and IOFF leakage characteristics of the GaN TFETs. GaN based devices have a superior relationship between on-resistance and breakdown voltage due to their higher critical electric field strength. This allows devices to be smaller and the electrical terminals closer together for a given breakdown voltage requirement.

Compared to silicon and Germanium based devices, GaN chips operate at higher voltages, frequencies and temperatures, helping to eliminate up to 90% of the power losses in electricity conversion. Wide bandgap refers to higher voltage electronic band gaps in devices, which are larger than 1 electron volt (eV). GaN devices are currently fabricated on different substrate materials, such as GaN on silicon (Si) and GaN on silicon carbide (SiC) wafers, with some debate about which process offers the best performance.

# 2. MODEL DERIVATION FOR GAN SIN-GLE GATE TFET

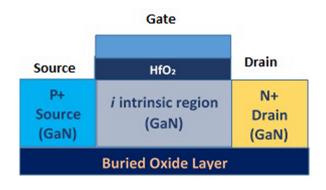

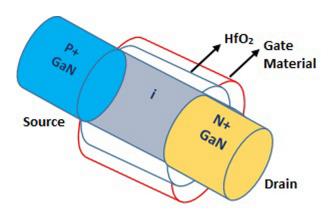

Fig. 1: Schematic diagram of Single Gate GaN

The cross sectional view of a GaN SG TFET is

TFET.

Manuscript received on May 28, 2014; revised on June 9, 2014

<sup>\*</sup> The authors are with National Engineering College, Kovilpatti, Tamilnadu, India, E-mail: arunsamuelece@nec.edu.in1, E-mail: armsece@gmail.com<sup>2</sup>

authors are with Dayananda Sagar Uni-Karnataka, versity, Bengaluru, India. Ē-mail : theodorechandra@gmail.com<sup>3</sup>

shown in Fig. 1. The source and drain are highly doped p-type and n-type regions respectively. The intermediate channel region comprises a moderately doped p-type layer.GaN can be doped with silicon (Si) or with oxygen[12] to n-type and with Magnesium [11] to p-type. The high-k material Hafnium oxide (HfO2) is used as the gate dielectric and the gate metal electrode work function is 4.05eV. The device parameters are listed in Table 1. On the operation of TFET, when the positive gate voltage VGS=1V is applied, the bands in the intrinsic region are move downwards and the tunneling barrier is formed between the p+ source region and lightly doped p type channel region. This reduced tunneling barrier width and the electric field near the tunneling junction will tunnel the electrons from the valance band of the source to the conduction band of the channel region. These generated electrons are transported to the drain through drift diffusion and gives the ION current

Table 1: The values of parameters used in simulations

| Quantities          | Symbol | value              |

|---------------------|--------|--------------------|

| Doping of source    | $N_A$  | $10^{20} cm^{-3}$  |

| Doping of drain     | $N_D$  | $10^{20} cm^{-3}$  |

| Metal work function | φ m    | $4.05 \mathrm{eV}$ |

| Oxide thickness     | tOX    | 2nm                |

| GaN body thickness  | R      | 20nm               |

| Channel length      | L      | 45 nm              |

# 2.1 Surface potential

The potential distribution in the gate oxide region is distinguished by two dimensional Poisson's equation.

$$\frac{\partial^2 \varphi(x,y)}{\partial x^2} + \frac{\partial^2 \varphi(x,y)}{\partial y^2} = \frac{qN_A}{\varepsilon_{GaN}} \tag{1}$$

Where q is the electronic charge,  $\varepsilon_{GaN}$  is the GaN permittivity.

The potential profile in the vertical direction is assumed to be a second-order polynomial, i.e.,

$$\varphi(x,y) = c_0(x) + c_1(x)y + c_2(x)y^2 \tag{2}$$

Here  $C_0(x)$ ,  $C_1(x)$  and  $C_2(x)$  are arbitrary constants. The Poisson's equation is solved using the following boundary conditions.

(a) Electric flux at the gate-oxide interface is continuous. Therefore

$$\frac{d\varphi(x,y)}{dy} = \frac{\varepsilon_{ox}}{\varepsilon_{GaN}} \frac{\varphi_s(x) - \psi_g}{t_{ox}} \text{aty} = 0$$

(3)

(b) Electric flux at the back gate-oxide and the back channel interface is continuous. Therefore

$$\frac{d\varphi(x,y)}{dy} = 0 \text{aty} = t_{GaN} \tag{4}$$

(c) The potential at the source end is

$$\varphi(0,0) = \varphi_s(0) = V_{bi} \tag{5}$$

(d) The Potential at the drain end is

$$\varphi(L,0) = \varphi_s(L) = V_{bi} + V_{DS} \tag{6}$$

Where,  $\psi_g = V_{GS} - \varphi_m + \chi + \frac{E_G}{2}$ EG is the energy gap.  $\chi$  is electron affinity of GaN,  $\phi_m$  is Gate metal work function,  $V_{GS}$  is Gate to source voltage.  $V_{DS}$  is Drain to source voltage.  $V_{bi}$ is the built in potential.  $\mathbf{t}_{GaN}$  is the Gallium Nitride body thickness and  $t_{ox}$  is the oxide thickness.

The constants  $C_0(x)$ ,  $C_1(x)$  and  $C_2(x)$  in equations (2) can be obtained from the boundary conditions (3) and (4) as described.

$$c_{0}(x) = \varphi_{s}(x)$$

$$c_{1}(x) = \frac{\varphi_{s}(x) - \psi_{g}}{t_{ox}} \frac{\varepsilon_{ox}}{\varepsilon_{GaN}}$$

$$c_{2}(x) = \frac{1}{2t_{s}} \frac{\varepsilon_{ox}}{\varepsilon_{GaN}} \frac{\psi_{g} - \varphi_{s}(x)}{t_{GaN}}$$

$$(7)$$

Substituting the values of  $C_0(x)$ ,  $C_1(x)$  and  $C_2(x)$ in equation (2) and using  $\phi(x,y)$  in equation (1) we obtain the potential distribution as

$$\varphi_s(x) = Ae^{\lambda x} + Be^{-\lambda x} + \psi_g \tag{8}$$

Where,  $\lambda = \sqrt{\frac{\varepsilon_{ax}}{\varepsilon_{GaN}t_{ox}t_{GaN}}}$  The coefficients A and B

are now expressed as,

$$A = \frac{-1}{2\mathrm{Sinh}(\lambda L)} [V_{bi} \exp(-\lambda L) - (V_{bi} + V_{DS}) + \psi_g (1 - \exp(-\lambda L)) + V_{DS}]$$

$$B = \frac{1}{2\mathrm{Sinh}(\lambda L)} [V_{bi} \exp(\lambda L) - (V_{bi} + V_{DS}) + \psi_g (1 - \exp(\lambda L)) - V_{DS}]$$

# 2.2 Electric field

The electric-field distribution along the channel length can be obtained by differentiating the surface potential. The electric field along the channel  $E_x$  can be written as

$$E_x = -\frac{d\varphi_s(x)}{dx} = -(A\lambda \exp(\lambda x) - B\lambda \exp(\lambda x))$$

(9)

The electric field in the vertical direction  $E_y$  can be written as

$$E_y = -\frac{d\varphi_s(x)}{dy} = -[C_1(x) + 2yC_2(x)]$$

(10)

#### 2.3 Drain Current

Finally,  $I_{DS}$  of TFETs can be calculated by integration band to-band tunneling (BBT) generation rate (G) over the channel region.

$$I_d = q \int G dx dy \tag{11}$$

For the calculation of Generation rate (G), Kane's Model has been employed [13] [14],

$$G(E) = A \frac{|E|^2}{\sqrt{E_G}} \exp[-B \frac{E_g^{3/2}}{|E|}]$$

(12)

Where, |E| is the magnitude of the electric field which is defined as  $|E| = \sqrt{E_x^2 + E_y^2}$  and EG is the energy band gap. The Parameters used for TCAD simulation are A=2.42\*10<sup>21</sup>eV<sup>1/2</sup>/cm.s.V<sup>2</sup> and B=15.7\*10<sup>6</sup>V/cm-(eV)<sup>3/2</sup>.

## 3. RESULTS OF GAN SINGLE GATE TFET

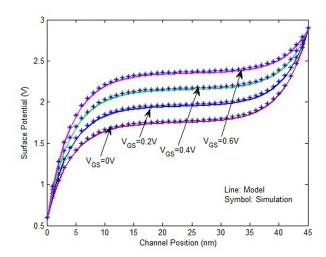

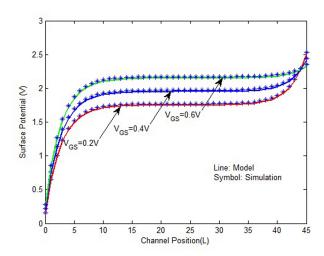

To verify the accuracy of the analytical model, twodimensional device simulation has been performed using TCAD Sentaurus. The model is tested on a TFET with a channel length of 45 nm, with different gate biasing. The variation of surface potential along the channel length L in the device for different applied gate voltages is illustrated in Figure 2 are obtained analytically by means of Equation (8). The potential remains constant in the middle of the GaN area while it varies across the source and drain junctions when the bias voltage  $V_{GS}=0$ . The potential variation is restricted to a small area near the tunneling junction as the biasing voltage is increased gradually. The reason for the potential being constant in the intrinsic region is attributed to the gates, and this forms the basic difference between the TFET and the p-i-n junction, with a constant electric field  ${f E}$  between the p-source and n-drain illustrated in Fig 2. Analytical results are in excellent agreement with TCAD results.

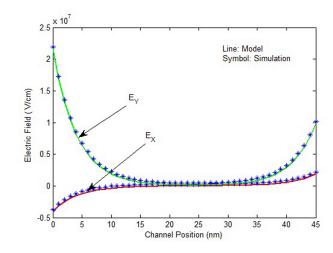

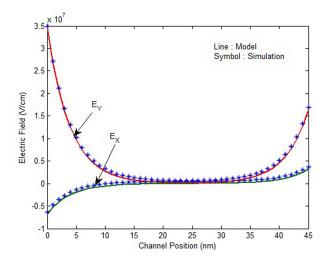

Fig. 3 shows that calculated and simulated values of lateral electric field  $E_X$  and Vertical Electric field  $E_Y$  with channel length  $L_{CH}$ =45nm of the SG TFET structure based on Equation (9) and (10). Lateral electric field is mainly contributed by the Drain to Source bias of the device. As the source-drain bias became more prominent and causes a raise in lateral electric field, it decreases the gate control over the channel. When gate voltage is varied, the lateral electric field remains constant at the channel region. It is clearly seen from the figure that the lateral electric field is less dominant on this device structure. Vertical electric field EY is mainly contributed by the gate to source voltage of the device. As the voltage applied to the gate increases, the high vertical electric field would be induced at the source to channel junction. Hence maximum vertical electric field is always present at the tunneling junction, this

Fig. 2: Surface potential profiles with variations of  $V_{GS}$  at  $V_{DS} = 0.5 V$ .

leads to reduced tunneling barrier width between the source region and intrinsic channel. Therefore, the reduced tunneling barrier width yields higher ION current performance. It can be seen that the Lateral electric field and vertical electric field distribution are in good agreement with simulation results.

Fig.3: Lateral Electric field  $(E_X)$  and Vertical electric field  $(E_Y)$  of SG-TFET for Channel length L=45nm and  $V_{DS}=0.5V$ .

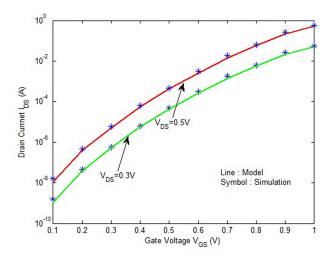

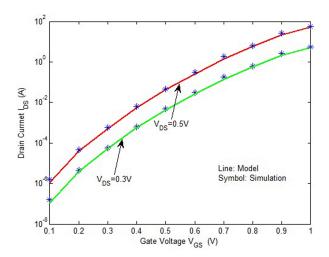

Fig. 4 shows the modeled and simulated values of  $I_{DS}$ - $V_{GS}$  characteristics of Single Gate TFET with drain voltages ( $V_{DS}$ ) 0.3V and 0.5V based on Equation (11). For the positive values of  $V_{GS}$ , electrons tunnel from valence band in p+ source region to conduction band in channel region and the tunneling current gets increased. In this condition, the device behaves as an n-type single gate TFET. Analytical results are in excellent agreement with simulation results.

Fig.4:  $I_{DS}$ - $V_{GS}$  Characteristics of SG TFET for channel length L=45nm with  $V_{DS}$ =0.3V and 0.5V.

# 4. MODEL DERIVATION FOR GAN GATE ALL AROUND TFET

The cross section view of a Gate all around TFET is shown in Figure 4. The coordinate system consists of a radial direction r, a vertical direction z, and an angular component  $\theta$  in the plane of the radial direction. The source and drain is made of highly doped p-type and n-type regions respectively. The intermediate channel region is made of a moderately doped n-type layer. HfO2 is used as the gate dielectric.

Fig. 5: Schematic diagram of GAA-TFET.

For the simplicity of derivation, it has been assumed that the TFET is operated in the subthreshold region where mobile carriers are negligible and that source-channel and drain-channel junctions are abrupt. No depletion in the source and drain region has been assumed. To obtain potential distribution throughout the device and the channel potential at the  $HfO_2$ -GaN interface, the 2-D Poisson's/Laplace Equation used is given as:

$$\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial\varphi\left(r,z\right)}{\partial r}\right) + \frac{\partial^{2}\varphi\left(r,z\right)}{\partial^{2}z} = \frac{qN_{A}}{\varepsilon_{GaN}}$$

(13)

To solve the 2-D Poisson's Equation for n channel surrounding gate TFET, the parabolic approximation approach is employed. The parabolic approach is applied to estimate the potential distribution over the 2-D space (along the device length and device depth) and the potential solution is given as:

$$\varphi(r,z) = C_0(z) + C_1(z)r + C_2(z)r^2 \tag{14}$$

Where the arbitrary constants  $C_0(z)$ ,  $C_1(z)$  and  $C_2(z)$  are functions of z only.

The boundary conditions required for the solution of Equation (13) are,

(a) The surface potential  $\phi_s(Z)$  is a function of z only.

$$\varphi(R, z) = s_1(z) = \varphi_s(z) \tag{15}$$

(b) The electric field in the center of the GaN pillar is zero.

$$\left. \frac{\partial}{\partial r} \varphi \left( r, z \right) \right|_{r=0} = 0 \tag{16}$$

(c) The electric field at the GaN /HfO2 interface is continuous.

$$\left. \frac{\partial \varphi \left( r,z \right)}{\partial r} \right|_{r=R} = \frac{\varepsilon_{ox}}{\varepsilon_{si} R} \left( \frac{\psi_{G} - \varphi_{s} \left( z \right)}{\ln \left( 1 + \frac{t_{ox}}{R} \right)} \right) \tag{17}$$

Here  $C_f = R \ln(1 + \frac{t_{ox}}{R})$

(d) The potential at the source end is

$$\varphi\left(0,0\right) = \varphi_{s}\left(0\right) = V_{bi} \tag{18}$$

(e) The potential at the drain end is

$$\varphi(r, L) = \varphi_s(L) = V_{bi} + V_{ds}$$

(19)

Where  $V_{bi}$  is the built in potential.  $V_{bi} = \frac{KT}{q} \ln \left( \frac{N_A N_D}{n_i} \right)$  $E_G$  is Band gap energy, q is elementary charge,

$E_G$  is Band gap energy, q is elementary charge,  $V_{GS}$  is Gate to Source voltage,  $V_{DS}$  is Drain to Source voltage,  $\varepsilon_{GaN}$  is relative permittivity of Gallium Nitride and  $\varepsilon_{ox}$  is relative permittivity of hafnium oxide.

Applying all the boundary conditions to equation (14), the coefficients  $C_0(z)$ ,  $C_1(z)$  and  $C_2(z)$  can be rewritten as functions of surface potential  $\varphi_s(z)$ , i.e.,

$$C_{0}(z) = \varphi_{s}(z) - \frac{R}{2} \frac{C_{f}}{\varepsilon_{si}} (\psi_{G} - \varphi_{s}(z))$$

$$C_{1}(z) = 0$$

$$C_{2}(Z) = \frac{1}{2R} \frac{C_{f}}{\varepsilon_{si}} (\psi_{G} - \varphi_{s}(z))$$

(20)

Substituting the equation (20) in (14), we get

$$\varphi\left(r,z\right)=\varphi_{S}\left(z\right)-\frac{R}{2}\frac{C_{f}}{\varepsilon_{Si}}\left(\psi_{G}-\varphi_{S}\left(z\right)\right)+\frac{1}{2R}\frac{C_{f}}{\varepsilon_{Si}}\left(\psi_{G}-\varphi_{S}\left(z\right)\right)r^{2} \eqno(21)$$

The surface Potential  $\varphi_s(z)$  can be obtained by solving the Poisson's equation (13) using (21).

$$\frac{d^{2}\varphi_{s}\left(z\right)}{dz^{2}}-K^{2}\varphi_{s}\left(z\right)=-K^{2}\psi_{G}\tag{22}$$

Where,

$$\begin{aligned} K^2 &= \frac{2C_f}{R\varepsilon_{si}} \\ \psi_G &= V_{GS} - \varphi_m + \chi + \frac{E_g}{2} \\ \text{By solving the second-order differential equations} \end{aligned}$$

(22), we get,

$$\varphi_s(z) = Ae^{Kz} + Be^{-Kz} + \psi_G \tag{23}$$

$\chi$  is the electron affinity. $\lambda$  is the characteristics length. This natural length is an easy guide for choosing device parameters.

The coefficients of A and B can be expressed as,

$$A = V_{bi} - \psi_G - \left\{ \frac{\left\{ e^{LK} V_{biS} - (V_{biD} + V_{DS}) \right\} - \left\{ e^{LK} 2 \psi_G \left( 2j \sinh\left(\frac{LK}{2}\right) \right) \right\}}{2j \sinh(LK)} \right\}$$

$$B = \left\{ (LK) \right\}$$

$$\frac{\left\{e^{LK}V_{biS} - (V_{biD} + V_{DS})\right\} - \left\{e^{LK}2\psi_G\left(2j\sinh\left(\frac{LK}{2}\right)\right)\right\}}{2j\sinh(LK)}$$

## 4.1 Electric Field

The electric-field distribution along the channel length can be obtained by differentiating the surface potential. The lateral electric field can be written as,

$$E_{z} = -\frac{\partial \varphi (r, z)}{\partial z} = \frac{\partial \varphi_{s} (z)}{\partial z} = K \left( A e^{Kz} - B e^{-Kz} \right)$$

(24)

The vertical electric field can be written as,

$$E_r = \frac{\partial \varphi (r, z)}{\partial r} = 2C_2(z)r \tag{25}$$

## 4.2 Drain Current

The flow of current  $I_{DS}$  in a surrounding gate TFET is based on Band-to-Band Tunneling (BTBT) of electrons from the valance band of the source to the conduction band of the channel region. The tunneling generation rate (G) can be calculated using Kane's model [13],[14]. The total drain current is then computed by integrating the band to band generation rate over the volume of the device.

$$I_{DS} = q\pi r^2 \iint G(r, z) dr dz \tag{26}$$

For the calculation of tunneling Generation rate (G), Kane's Model has been employed [13], [14]

$$G(E) = A_{kane} \frac{|E|^2}{\sqrt{E_g}} e^{\left[-B_{kane} \frac{E_g^{3/2}}{|E|}\right]}$$

(27)

Where,

$$B_{kane} = \frac{q^2 \sqrt{2m_{tunnel}}}{h^2 \sqrt{E_g}}$$

$$\frac{1}{m_{tunnel}} = \frac{1}{m_h m_0} + \frac{1}{mem_0}$$

|E| is the magnitude of the electric field which is defined as  $|E| = \sqrt{E_r^2 + E_z^2}$  and  $E_g$  is the energy band gap.  $m_0$  is the rest mass of an electron,  $m_e$  and  $m_h$ are the electron and hole effective masses respectively.

#### 5. RESULTS OF GAN GAA-TFET

Fig. 6 shows the calculated surface potential profile for different gate voltage of Gate All Around TFET structure along with the simulated potential profile, which is analytically obtained by Equation (23). As the gate voltage increases, the potential in the lightly doped region increases. The analytical results have been compared with the TCAD simulated results and a good agreement is achieved.

Fig. 6: Surface potential profiles of GaN based GAA-TFET for Channel Length L=45nm and  $V_{DS}=0.1V$ with different gate biases.

Fig. 7 shows the calculated and simulated values of vertical electric field distribution along the channel length, which is analytically obtained by Equation (24) and (25). It is evident from the figure that the peak of the vertical electric field appears near the source side. This leads to increase in tunneling generation rate. Due to this effect, the tunneling current gets increased. From the results, it is clearly understood that the calculated values of the analytical model tracks the simulated values very well.

Fig. 8 shows the  $I_{DS}$ - $V_{GS}$  characteristics of GaN based SG TFETs. The work function of the gate

**Fig.7:** Lateral Electric field (EX) and Vertical electric field ( $E_Y$ ) of GAA-TFET for Channel length L=45nm and  $V_{DS}=0.5V$ .

Fig.8:  $I_{DS}$ - $V_{GS}$  Characteristics of GAA TFET for channel length L=45nm with  $V_{DS}$ =0.3V and 0.5V.

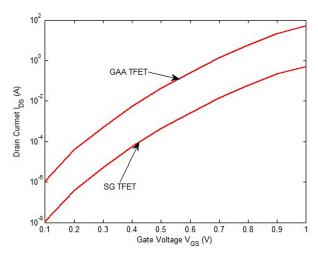

metal for SG TFET is chosen as 4.5 eV. As shown in the figure, the drain current increases with increasing gate-source bias. Furthermore, the comparative analysis of GaN based SG-TFET and GAA TFET devices is done and the outcome is shown in Fig. 9. From this figure, it is clear that, GaN based GAA TFET has more advantage compare to the SG TFET, in terms of its higher  $I_{ON}$  current

#### 6. CONCLUSION

In this work, an attempt has been made to develop 2D models for analyzing surface potential, electric field along the channel, vertical electric field and drain current for GaN based SG TFET and GAA TFET. The results obtained clearly show that GaN based GAA TFET has more advantage compare to the SG TFET, in terms of its higher  $I_{ON}$  current. The an-

Fig. 9:  $I_{DS}$ - $V_{GS}$  Characteristics comparison of SG TFET and GAA TFET for channel length L=45nm with  $V_{DS}$ = 0.5V.

alytical results have been compared with the TCAD simulated results and a good agreement is achieved between both of them. This research can be extended further by doing elaborate studies.

#### References

- [1] R. Li et al., "AlGaSb/InAs tunnel field-effect transistor with on-current of 78  $\mu$ A/ $\mu$ m at 0.5 V," in *IEEE Electron Device Lett.*, vol. 33, no. 3, pp. 363-365, Mar. 2012.

- [2] A. Vandooren et al., "Analysis of trap-assisted tunneling in vertical Si homo-junction and SiGe hetero-junction tunnel-FETs," in *Solid-State Electron.*, vol. 83, pp. 50-55, May 2013.

- [3] S. Brocard, M. Pala, and D. Esseni, "Design options for heterojunction tunnel FETs with high on current and steep sub-VT slope," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 2012, pp. 5.4.1-5.4.4.

- [4] M. Kim, Y. K. Wakabayashi, M. Yokoyama, R. Nakane, M. Takenaka, and S. Takagi, "Ge/Si heterojunction tunnel field-effect transistors and their post metallization annealing effect," in *IEEE Trans. Electron Devices*, vol. 62, no. 1, pp. 9-15, Jan. 2015.

- [5] W. Li, S. Sharmin, H. Ilatikhameneh, R. Rahman, Y. Lu, J. Wang, X. Yan, A. Seabaugh, G. Klimeck, D. Jena, and P. Fay, "Polarization engineered III-nitride heterojunction tunnel field-effect transistors," in *IEEE J. Exploratory Solid-State Comput. Devices Circuits*, vol. 1, no. 1, pp. 28-34, Dec. 2015.

- [6] Alan Seabaugh; Sara Fathipour; Wenjun Li; Hao Lu; Jun Hong Park; Andrew C. Kummel; Debdeep Jena; Susan K. Fullerton-Shirey; Patrick Fay, "Steep subthreshold swing tunnel FETs:

GaN/InN/GaN and transition metal dichalcogenide channels 2015," in *IEEE International Electron Devices Meeting (IEDM) 2015*, pp. 35.6.1-35.6.4.

- [7] TS Arun Samuel, NB Balamurugan, Sibitha,S, "Analytical Modeling and Simulation of Dual Material Gate Tunnel Field Effect Transistors," in *Journal of Electrical Engineering & Technol*ogy, vol. 8, no. 6, pp. 1481-1486.

- [8] TS Arun Samuel, NB Balamurugan, "An Analytical Modeling and Simulation of Dual Material Double Gate Tunnel Field Effect Transistor for Low Power Applications," in *Journal of Electrical Engineering & Technology*, vol. 9, no. 1, pp. 247-253.

- [9] TS Arun Samuel, NB Balamurugan, Niranjana, "Analytical Surface potential model with TCAD simulation verification for evaluation of Surrounding Gate TFET," in *Journal of Electrical Engineering & Technology*, Vol. 8, pp. 742-748, 2013

- [10] Eng-Huat Toh, Grace Huiqi Wang, et al., "Device physics and design of germanium tunnelling field-effect transistor with source and drain engineering for low power and high performance applications," in *Journal of Applied Physics*, 103(10):104504, 2008.

- [11] Wetzel, C.; Suski, T.; Ager, J.W. III; Fischer, S.; Meyer, B.K.; Grzegory, I.; Porowski, S., "Strongly localized donor level in oxygen doped gallium nitride," in *International conference on physics of semiconductors*, Berlin (Germany), 21âĂS26 July 1996.

- [12] Hiroshi Amano, Masahiro Kito, Kazumasa Hiramatsu and Isamu Akasak, "P-Type Conduction in Mg-Doped GaN Treated with Low-Energy Electron Beam Irradiation (LEEBI)," in Japanese Journal of Applied Physics, Volume 28, Part 2, Number 12 1989.

- [13] EO Kane, "Zener tunneling in semiconductors," in *Journal of Physics and Chemistry of Solids*, vol. 12, no. 2, pp.181-188, 1960.

- [14] EO Kane, "Theory of tunneling," in *Journal of Applied Physics*, vol. 32, no. 1, pp. 83-91, 1961.

IAENG and member of IEEE. His research interest includes Modeling and Simulation of Multi gate transistors and Tunnel Field effect Transistors.

N. Arumugam received B.E degree in Electronics and Communication Engineering (1986) from Maurai Kamaraj University and M.E in Electron Devices (1994) from Jadavpur University Kolkata. Currently working in National Engineering College, Kovilpatti, India as Associate Professor and pursuing Ph.D in Information and Communication Engineering. He has teaching experience of more than 29 years.

His research interest includes VLSI, Embedded systems and Nanoscale Device Modeling and Simulation.

Theodore Chandra is currently working as Assistant Professor, Department of ECE, School of Engineering, Dayananda Sagar University, Bangalore, India. He received his Ph.D from Anna University, Chennai. He has completed his Bachelor of Engineering in Electronics and Communication Engineering and Masters of Engineering with specialization in Communication Systems from Anna University, Chennai. His research

interest includes semiconductor device modeling and simulation, high electron mobility transistors and nanowire transistors. He is a recipient of Senior Research Fellowship from the Council of Scientific and Industrial Research (CSIR), Government of India, New Delhi. He has five years of research experience and has published six research papers in international journals which are SCI indexed. He has presented five research papers in international and national conferences. He is a member of technical societies like IEEE, ECS, IEICE and IAENG. He has completed a CEP course on "Semiconductor Technology and Manufacturing" conducted by IIT Bombay. He is a certified trainer for the Centre of Competence for Automation Technologies - Joint Initiative of Bosch Rexroth & Dayananda Sagar University.

T.S. Arun Samuel received B.E degree in Electronics and Communication Engineering from Syed Ammal Engineering College (2004) and M.E degree in Computer and communication engineering from National Engineering College (2006). He has awarded Ph.D on Nano electronic Devies (2014) from Thiagarajar College of Engineering, Tamilnadu, India under Anna University Chennai. Currently working in National

Engineering College, Kovilpatti, India as Assistant Professor (Senior Grade). He has authored more than 18 research articles in National & International Journals and Conferences. He is the life member of Institute of Engineering (IE), India,