## Cascode Current Mirror for a Variable Gain Stage in a 1.8 GHz Low Noise Amplifier (LNA)

Lini Lee<sup>1</sup>, Roslina Mohd Sidek<sup>2</sup>, Sudhanshu Shekhar Jamuar<sup>3</sup>, and Sabira Khatun<sup>4</sup>, Non-members

#### ABSTRACT

A high frequency CMOS variable gain low noise amplifier (VGLNA) constructed based on an inductive source degenerated LNA and a cascode current mirror is proposed. The 'variable' concept is to prevent the unwanted saturation phenomenon due to large input signal. A cascode current mirror cell which consumes minimal voltage headroom without sacrificing the accuracy of the circuit is proposed in the circuit. With a 0.18 m CMOS technology, this technique is applied on a VGLNA operating at 1.8 GHz for GSM band application. The simulation results reveal that the maximum gain is 17.29 dB with gain tuning range of 9.56 dB. The noise figure (NF) is less than 0.92 dB with the power consumption of 9.34 mW at power supply of 1.8 V. Comparison with several same operating frequency LNA circuits published show that this work demonstrated among the lowest NF and highest IIP3 with compromise on the gain.

**Keywords**: cascode current mirror, low noise amplifier, noise figure, variable gain

## 1. INTRODUCTION

Current sources are widely used in amplifiers, either single-stage or differential amplifiers. In these circuits, current source acts as a large resistor without consuming excessive voltage headroom. Some digital-to-analog converters (DAC) employed an array of current sources to produce an analog output proportional to digital input signal. Current sources, in conjunction with "current mirrors" can perform useful functions in analog signals. Some modifications to a current mirror, act as a low voltage cell can bring in lots of advantages to the analog design especially in the wireless communication field. With the trend towards fully integrated wireless transceivers which demand portable and low power consumption

devices [1], a breakthrough of design techniques in transceivers is highly desirable.

This paper presents a design of variable gain stage utilizing a cascode current mirror as a low voltage cascode cell for a variable gain low noise amplifier (VGLNA). A variable gain in an LNA is to prevent saturation of the receiver when the input signal is relatively large. There has been several gain control techniques presented, such as using a bypass switch in the main amplifier and achieving different gain levels [2]. However, the gain, linearity and the return loss are no longer controllable parameters and the switch path may induce losses. Another popular method is splitting a portion of current from the amplifier [3-4]. However, in this technique, the return loss becomes worse and higher noise is introduced in low gain mode.

In this paper, a high frequency VGLNA employing a cascode current mirror which could eliminate the accuracy and voltage headroom trade-off to achieve gain control is presented. This work demonstrates a CMOS VGLNA working at 1.8 GHz frequency band, capable to achieve gain control as well as maintaining its input and output return loss in different mode (high gain and low gain modes) without degrading the noise performance.

# 2. VARIABLE GAIN LOW NOISE AMPLIFIER CIRCUIT DESIGN

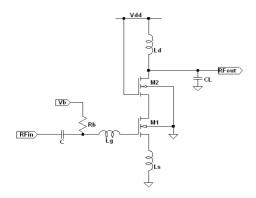

Among the common structure of single-ended amplifiers, namely, resistive termination, 1/gm termination, shunt-series feedback and inductive source degeneration, the last one has the best noise performance. Here, a single stage cascode LNA with inductive source degeneration topology is used, as shown in Fig. 1. A single-stage topology is chosen to minimize the power dissipation and to improve third-order intercept point (IP3) performance.

In this paper, the proposed VGLNA can meet two merits, the unconditional stability in each stage and low power consumption. The LNA is the first functional block in a wireless receiver. At the early stage of a receiver, the noise figure (NF) of the LNA is the dominant issue as the received signal is very small. However, as the received signal becomes large, the IIP3 becomes an important parameter to prevent the

Manuscript received on January 25, 2007; revised on August 37, 2007.

<sup>1,2,3,4</sup> The authors are with Department of Electrical & Electronic Engineering, Faculty of Engineering, University Putra Malaysia (UPM), 43400 UPM Serdang, Selangor, Malaysia, E-mail: linilee@gmail.com, roslina@eng.upm.edu.my, ssjamuar@eng.upm.edu.my, sabira@eng.upm.edu.my

Fig.1: Cascode Low Noise Amplifier (LNA) with Inductive Source Degeneration Structure.

receiver from reaching saturation. Therefore, a cascode current mirror is added to act as the variable gain stage, completing the gain-adjustable mechanism [5].

#### 2.1 Inductive Source Degenerated LNA

There are a few existing LNA papers which has been presented in the range of frequency between 1.6 - 3.0 GHz. An LNA microwave monolithic integrated circuit (MMIC) has been implemented in silicon-oninsulator (SOI) CMOS technology with just a drain voltage of 0.6 V, giving the Gain/Power quotient of 5.33 dB/mW [6]. This amplifier is matched internally using two spiral inductors and a capacitor. By inserting just a single inductor acting as an inter-stage matching network, a 2-GHz LNA can also be optimized [7]. On the other hand, a high-Q active inductor is introduced into a 1.75-GHz CMOS LNA to reduce the area of chip and the complexity [8]. The chip area which is often occupied with integrated passive inductor is usually large compared to other components. Hence, an active inductor implemented from a gyrator has been proposed. As for the multiband purpose, an LNA using positive feedback to improve its gain has been presented [9]. The use of positive feedback improves the gain compared to all of the other common-gate LNA topologies. Another LNA topology worth mentioning is the CMOS LNA operating at subthreshold region with one of the best overall figure of merit (FOM) [10]. All these LNAs were optimized for performance in terms of supply voltage, power consumption and NF. However, none has yet explore the possibility of providing gain variation to the existing structures of LNA like the source degenerated structure. This could save cost with the existing LNAs and with the gain variation; this could prevent saturation of the receivers if the input signal is too large.

Therefore the inductive source degenerated LNA topology as shown in Fig. 1 is adapted to be used as variable-gain LNA or VGLNA due to its minimum

NF which uses a source degenerative inductor to realize input impedance matching [5]. The circuit is optimized to work at the resonance frequency of 1.8 GHz with the input impedance written as

$$Z_{in} = s(L_s + L_g) + \frac{1}{sC_{gs}} + \left(\frac{g_m}{C_{gs}}\right)L_s \tag{1}$$

where  $g_m$  is the device transconductance and  $C_{gs}$  is the gate-to-source capacitance. At the frequency of operation, value of  $L_s$  can be chosen in order for the real term to be made equal to 50  $\Omega$  bringing impedance matching to the input stage. For the power matched at resonance, the real part of input impedance need to be equalled to source resistance. For the noise factor (F) calculation, the size of the input transistor is chosen such that it minimizes the noise based on the following expression [5]:

$$F_{min} \cong 1 + \sqrt{\frac{4}{5}} \frac{\omega}{\omega_T} \sqrt{\gamma \cdot \delta \cdot (1 - |c^2|)}$$

(2)

where  $\omega_T = g_m/C_{gs}$ , the unity gain frequency with gm is the transistor transconductance and  $C_{gs}$  is the gate source capacitor.  $\gamma = 3/2$  is the channel thermal noise, c is the complex correlation term which is equal to j0.395,  $\delta = 4/3$  is the coefficient of gate noise. As observed from (2),  $F_{min}$  is effective for  $\omega < \omega_T$  and the noise factor increases with frequency. Owing to the down scale of CMOS process, the  $\omega_T$  would raises, allowing circuits to operate at higher frequency while maintaining the minimum noise factor. It is noted that the noise parameters:  $\gamma, \delta$  and c in the above calculation are considered independent of the bias voltage.

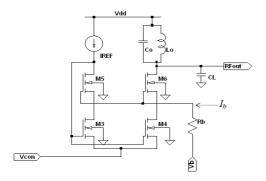

The key property of a current mirror is to allow precise copying of the current with no dependence on process and temperature. Therefore, to suppress these dependence like the channel-length modulation, a cascode current mirror as shown in Fig. 2 that have identical drain-source voltage and a high output resistance is proposed. These transistors are in saturation and proper rationing ensures that  $VGS5 = V_{GS6}$ . If

$$V_{con} = V_{GS5} + (V_{GS3} - V_{TH3})$$

=  $V_{GS6} + (V_{GS4} - V_{TH4})$  (3)

then the cascode current source M4 and M6 consumes minimum headroom (the overdrive of M4 plus that of M6) while M3 and M4 sustain equal drain-source voltages, allowing accurate copying of  $I_{REF}$ . The voltage,  $V_{con}$  is the voltage that flows from the LNA stage to the cascode current mirror.

In this work, the cascode current mirror is used to achieve gain control function. Referring to Fig. 2, the cascode current mirror is comprised of transistors M3-M6, a reference current,  $I_{REF}$  and bias voltage,

$V_b$ . These transistors are controlled through changes in the bias resistance,  $R_b$  which influences the current,  $I_b$  flowing through the transistors M5 and M6. At the source terminal of M3 and M4, voltage,  $V_{con}$  flows from the LNA stage with the DC signal blocked by a DC blocking capacitor  $C_{bl}$  while steering the RF signal into the current mirror. Thus, by changing  $R_b$ , taking a constant  $V_b$  divided by  $R_b$ , a set of current values,  $I_b$  is produced.

For this analysis,  $R_b$  remained constant and  $V_b$  is being varied from 1.0 to 1.8 V resulting in gain variation with the range of 9.56 dB. The advantage of this gain controlled mechanism is that the gain variation is achieved without degrading the noise performance since there are constructed from two different stages.

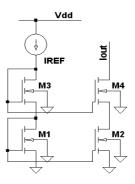

Comparing this structure with the traditional cascode current mirror in Fig. 3, the minimum allowable voltage is two overdrive voltage plus one threshold voltage as shown here,

$$V_{con} = V_{GS1} + V_{GS3} (4)$$

Comparing (4) and (3), one threshold voltage is "wasted" in the voltage headroom of the current mirror [11]. Therefore, in this work, the proposed cascode mirror with two overdrive voltage headroom as shown in Fig. 2 is termed as "low-voltage cascode" and implemented as variable gain stage.

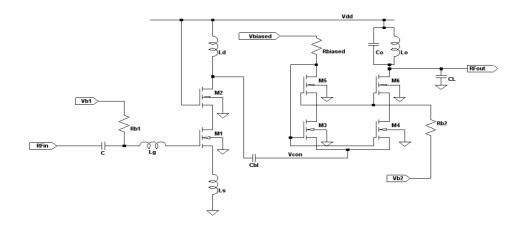

Combining the circuits of Fig. 1 and 2, a VGLNA based on inductive source degenerated structure is proposed as shown in Fig. 4. The VGLNA is designed to work at 1.8 GHz and it is simulated to meet the best desired requirements. However, there is a drawback with the need of using a higher biased voltage,  $V_{biased}$  at approximately 3.0 V for the variable gain stage. Nevertheless, the power consumption stays at 9.34 mW.

At the output, the inductor  $L_o$  and capacitor  $C_o$  are chosen to match the output impedance. This formed an output LC-tank circuit which is used to tune the VGLNA to the resonance frequency.

Fig.2: Proposed Cascode Current Mirror as Variable Gain Stage.

Fig.3: Cascode Current Mirror with voltage headroom consumed.

## 3. SIMULATION RESULTS

The complete VGLNA was simulated with parameters from a standard 0.18- $\mu$ m CMOS process technology using Agilent's Advanced Design System (ADS). The transistors width, inductors and capacitors values are shown in Table I and the minimum length of the transistors is 0.22  $\mu$ m. The control voltage of  $V_{b2}$  ranged from 1.0 to 1.8 V and the supply voltage  $V_{dd}$  is 1.8 V.

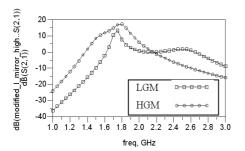

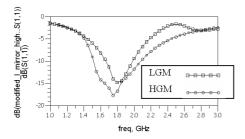

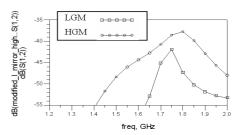

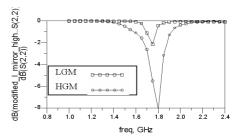

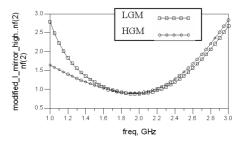

The Fig. 5 to 9 show the simulation results for S21, S11, S12 and S22 where the amplifier is tuned around 1.8 GHz at high gain mode (HGM) and low gain mode (LGM) respectively. HGM is achieved when the control voltage is applied at 1 V while the LGM is achieved when  $V_{b2} = 1.8$  V. It can be seen that S21 is 17.29 dB at HGM and 7.73 dB at LGM. In the HGM, the input return loss or S11 is -16.67 dB while in the LGM, it is equalled to -14.78 dB. In Fig. 7, it shows that the reverse isolation S12 at the HGM is better than the LGM with the overall reverse isolation less than -38 dB. As for the output return loss, the S22 results are shown in Fig. 8. In Fig. 9, the NF is achieved at 0.92 dB regardless of operating in HGM or LGM. As for the two tones testing, two tones are located at 1.80 GHz and 1.82 GHz with the power level of -20 dBm. The third-order input intercept point (IIP3) simulated are 6.34 dBm and 5.59 dBm at HGM and LGM respectively. The power consumed by the VGLNA at power supply of 1.8 V is simulated to be 9.34 mW at both modes.

Table II shows the performance of this work and comparison with several 1.8 GHz LNA circuits published [12, 13]. However, the performances of the LNA in [6, 12] are measured values while in [13] the results are simulated values. To compare overall performance of the LNAs, the gain over power quotient and figure of merit (FOM) based on [10] has been used. It is observed that this work demonstrated the lowest NF and highest Gain/Power quotient. This VGLNA has the best FOM with the reasonable power consumption as compared to LNA in [6].

Fig.4: Schematic of the Proposed VGLNA.

Table 1: Component values and device dimensions.

| Parameters          | Value                |

|---------------------|----------------------|

| $ m W_{M1}$         | $190 \mu \mathrm{m}$ |

| $ m W_{M2}$         | $60\mu\mathrm{m}$    |

| $ m W_{M3}$         | $410 \mu \mathrm{m}$ |

| $ m W_{M4}$         | $20\mu\mathrm{m}$    |

| $ m W_{M5,M6}$      | $500 \mu \mathrm{m}$ |

| $L_{ m g}$          | 10.8nH               |

| $L_{s}$             | $0.9 \mathrm{nH}$    |

| $L_{\mathrm{d}}$    | 14.8nH               |

| $L_{o}$             | 1.8nH                |

| $C_{o}$             | 3.8pH                |

| $\mathrm{C_{L,in}}$ | 0.5pH                |

Fig.5: Voltage Gains in the Low Gain Mode (LGM) and High Gain Mode (HGM).

Fig.6: S11 of the Proposed VGLNA in Low Gain Mode (LGM) and High Gain Mode (HGM).

Fig. 7: S12 of the Proposed VGLNA in Low Gain Mode (LGM) and High Gain Mode (HGM).

Fig.8: S22 of the Proposed VGLNA in Low Gain Mode (LGM) and High Gain Mode (HGM).

Fig.9: Noise Figure (NF) of the Proposed VGLNA in Low Gain Mode (LGM) and High Gain Mode (HGM).

| Table | 2: | Comparison | of | several | 1.6 | - | 1.8 | GHz |

|-------|----|------------|----|---------|-----|---|-----|-----|

| LNAs. |    |            |    |         |     |   |     |     |

| Descriptions     | This   | [6]  | [12]  | [13]  |

|------------------|--------|------|-------|-------|

|                  | work   |      |       |       |

| Supply voltage   | 1.8    | 0.6  | 1.5   | 3.0   |

| (V)              |        |      |       |       |

| $Process(\mu m)$ | 0.18   | 0.35 | 0.25  | 0.8   |

| Operating        | 1.8    | 1.6  | 1.8   | 1.8   |

| frequency        |        |      |       |       |

| (GHz)            |        |      |       |       |

| NF(dB)           | 0.92   | 4.2  | 5     | 2.1   |

| Gain(dB)         | 17.29  | 10.8 | 14.1  | 18.0  |

| IIP3(dBm)        | 6.34   | 12   | -7.6  | -5    |

| S11(dB)          | -16.67 | -    | -23.5 | -     |

| Power            | 9.34   | 7.5  | 30    | 48    |

| consumption      |        |      |       |       |

| (mW)             |        |      |       |       |

| $Gain/P_{dc}$    | 1.85   | 1.44 | 0.47  | 0.375 |

| FOM              | 22.83  | 14   | -1.52 | -2.78 |

## 4. CONCLUSIONS

A 1.8 GHz VGLNA has been designed in 0.18 m CMOS process for GSM application. The VGLNA uses a modified cascode current mirror technique to achieve gain control function. Only minimal voltage headroom is required in the cascode current mirror for the variable gain stage. Regardless of gain modes, the VGLNA achieves NF of less than 0.92 dB with input return loss of -16.67 and -14.78 in HGM and LGM respectively. Operating at 1.8 V supply voltage, the circuit provides a maximum gain of 17.29 dB and a minimum gain of 7.73 dB. In the linearity response, the VGLNA acquires IIP3 of 6.34 dBm in HGM. The proposed VGLNA offers a compromise between gain, NF and linearity. The simulated results fulfil the specifications for a 1.8 GHz LNA design. Thus, this VGLNA can be used to achieve amplification in a wireless receiver front-end which requires a fully integrated, low noise and low power consumption architectures.

## 5. ACKNOWLEDGEMENT

This research is supported by Ministry of Science, Technology and Innovation (MOSTI) of Malaysia through National Science Fellowship (NSF) and Silterra (M) Sdn. Bhd..

#### References

- [1] C. Guo, et al., "A fully integrated 900-MHz CMOS wireless receiver with on-chip RF and IF filters and 79-dB image rejection," *IEEE J. Solid-State Circuits*, Vol. 37, pp 1084–1089, 2002.

- [2] R. Point, M. Mendes, W. Foley, "A Differential 2.4 GHz Switched-Gain CMOS LNA for

- 802.11b and Bluetooth," *IEEE Radio and Wireless Conference 2002*, RAWCON 2002, pp. 221–224, Aug. 2002.

- [3] E. Sacchi, I. Bietti, F. Gatta, F. Svelto and R. Castello, "A 2 dB NF, fully differential, variable gain, 900 MHz CMOS LNA," Symp. On VLSI Circuits 2000, pp. 94–97, June 2000.

- [4] K. L. Fong, "Dual-band High Linearity Variable-Gain Low Noise Amplifiers for Wireless Applications," Digest of Technical Papers IEEE Solid-State Circuits Conference 1999, pp. 224–225, Feb 1999.

- [5] T. H. Lee, The design of CMOS Radio Frequency Integrated Circuit, 2nd ed., Cambridge University Press, 1998.

- [6] K. Ohsato and T. Yoshimasu, "Internally Matched, Ultralow DC Power Consumption CMOS Amplifier for L-Band Personal Communications," *IEEE Microwave and Wireless Com*ponents Letters, Vol. 14, No. 5, pp. 204–206, May 2004.

- [7] C. Zhang, D. Huang and D. Lou, "Optimization of Cascode CMOS Low Noise Amplifier using Inter-stage Matching Network," *IEEE Conf. on Electron Devices and Solid-State Circuits*, pp.465–468, Dec 2003.

- [8] J.-N. Yang, et. al., "A 1.75 GHz Inductor-less CMOS Low Noise Amplifier with High-Q Active Inductor Load," Proc. of 44th IEEE 2001 Midwest Symp. on Circuits and Systems, Vol. 2, pp. 816–819, Aug 2001.

- [9] A. Liscidini, et. al., "A 0.13 m CMOS Front-End, for DCS1800/UMTS/802.11b-g with Multiband Positive Feedback Low-Noise Amplifier," *IEEE Journal of Solid-State Circuits*, Vol. 41, No. 4, pp. 981–989, April 2006.

- [10] H. Lee and S. Mohammadi, "A 3GHz Subthreshold CMOS Low Noise Amplifier," *IEEE Radio Frequency Integrated Circuits Symp. 2006*, pp.4, June 2006.

- [11] D. A. Johns and K. Martin, Analog Integrated Circuit Design, John Wiley & Sons, Inc., 1997.

- [12] S-. K. Tang, C-. F. Chan, C-. S. Choy and K-. P. Pun, "CMOS RF LNA with high ESD immunity," Proc. IEEE Asia Pacific Conf. on Circuits and Systems, Vol. 1, pp. 321–324, Dec 2004.

- [13] S. Park and W. Kim, "Design of a 1.8 GHz Low-noise Amplifier for RF Front-end in a 0.8 m CMOS technology," *IEEE Trans. Consumer Electronics*, Vol. 47, No. 1, pp. 10–15, Feb 2001.

Lini Lee received her M.Sc. degree in electronic engineering in 2001 from Universiti Putra Malaysia (UPM), Serdang, Malaysia. From 2001 to 2004, she worked in the electronic engineering industry, involved in design services especially in ASIC designs, giving supports and trainings to engineers. She is currently pursuing her Ph.D degree in RF CMOS IC design at UPM, Serdang, Malaysia. She is a student member of

Malaysia. She is a student member of IEEE and her research interests include ASIC and RFIC designs. E-mail: linilee@gmail.com

Roslina Mohd Sidek received her B.Sc. (Electrical Engineering) degree from George Washington University, Washington D.C, USA in 1990. She received M.Sc (Microelectronics Systems Design) degree in 1992 and Ph.D degree in 1999 from University of Southampton, UK. She is currently a lecturer in the department of Electrical and Electronic Engineering, Universiti Putra Malaysia. Her research interests

tra Malaysia. Her research interests include semiconductor devices and IC design. E-mail: roslina@eng.upm.edu.my

S.S. Jamuar received his M. Tech and Ph. D. in Electrical Engineering from Indian Institute of Technology, Kanpur, India in 1970 and 1977 respectively. He has been teaching and conducting research in the areas of Electronic Circuit Design, Instrumentation and Communication Systems. Presently he is Professor in the Electrical and Electronic Engineering Department in the Faculty of Engineering, University Putra Malaysia

(Malaysia) since 2001. He is senior member of IEEE and Fellow of Institution of Electronics and Telecommunications Engineering (India). He is on the Editorial Board of Wireless Personnel Communication Journal. He is presently the Chapter Chair for IEEE CAS Chapter in Malaysia. E-mail: ssjamuar@eng.upm.edu.my

Sabira Khatun received her B.Sc (Hons.), M,Sc in Applied Mathematics and PhD on Hydromagnetic Stability from the University of Rajshahi, Bangladesh in 1988, 1990 and 1994 respectively. She received her second PhD in communications and Networking from University Putra Malaysia (UPM) in 2003. She became a Lecturer at the Discipline of Computer Science and Engineering, Khulna University (KU),

Bangladesh in 1991 followed by Assistant Professor in KU in 1994 and Senior Lecture in UPM in 1998. Presently she is working as Associate Professor at the Department of Computer & Communication Systems Engineering, University Putra Malaysia. She is an active researcher of Teman project and MyREN Research Community. She is a member of IEEE and her research interest spans Broadband and Wireless Communications, Software Defined Radio and IPv6. E-mail: sabira@eng.upm.edu.my