# Digital Robust Control for DC-DC Converter with Second-Order Differential Characteristics

Kohji Higuchi<sup>1</sup>, Eiji Takegami<sup>2</sup>, Kazushi Nakano<sup>3</sup>, Tatsuyoshi Kajikawa<sup>4</sup>, Satoshi Tomioka<sup>5</sup>, Non-members, and Kosin Chamnongthai<sup>6</sup>, Member

#### ABSTRACT

Robust DC-DC converter which can covers extensive load changes and also input voltage changes with one controller is needed. The demand to suppressing output voltage changes becomes still severer. We proposed an approximate 2DOF digital controller which realizes the startup response and dynamic load response independently. The controller makes the control bandwidth wider, and at the same time makes a variation of the output voltage small at sudden changes of loads and input voltages. In this paper, a new approximate 2DOF digital control system with additional zeros is proposed. Using additinal zeros second-order differential transfer characteristics between equivalent disturbances and an output voltage are realized. Therefore the new controller makes variations of the output voltage smalerl at sudden changes of loads and input voltages. This controller is actually implemented on a DSP and is connected to a DC-DC converter. Experimental studies demonstrate that this type of digital controller can satisfy given severe specifications.

**Keywords**: DC-DC converter, Approximate 2DOF, Second-order differential, Digital robust control

### 1. INTRODUCTION

In many applications of DC-DC converters, loads cannot be specified in advance, i.e., their amplitudes are suddenly changed from the zero to the maximum rating. Generally, design conditions are changed for each load and then each controller is re-designed. Then, a so-called robust DC-DC converter which can cover such extensive load changes and also input voltage changes with one controller is needed. Analog

control IC is used usually for control of DC-DC converter. Simple integral control etc. are performed with the analog control IC. Moreover, the application of the digital controller to DC-DC converters designed by the PID or root locus method etc. has been recently considered[1], [2]. However, it is difficult to retain sufficient robustness of DC-DC converters by these techniques. Various robust control methods for improving start-up characteristics and load sudden change characteristics of DC-DC converters are proposed[3], [4], [5], [6], [7]. However, they take tens [ms] for the rise time of the startup responses, and hundreds [mV] output voltage regulations have arisen in the load sudden changes. The demand for suppressing output voltage change becomes still severer, and the further improvements to startup characteristics and load sudden change characteristics are required. The authors proposed the method of designing an approximate 2-degree-of-freedom (2DOF) controller of DC-DC converter[8], [9], [10], [11]. This controller realized first-order differential transfer characteristics between equivalent disturbances and an output voltage. Therefore, there is a limit in suppressing the output voltage variation, and the variation was not able to be made smaller.

In this paper, we propose a new approximate 2DOF digital controller which realizes second-order differential transfer characteristics[12], [13]. These characteristics are realized by introducing additional zeros into transfer functions between equivalent disturbances and the output. The new controller makes the variations of the output voltage smaller than the former controller[11] at sudden changes of resistive loads and input voltages. A new DC-DC converter equipped with the proposed controller in DSP is actually manufactured. Some simulations and experiments show that this new DC-DC converter can satisfy given severe specifications.

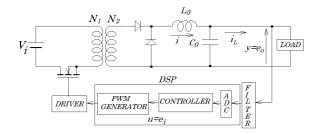

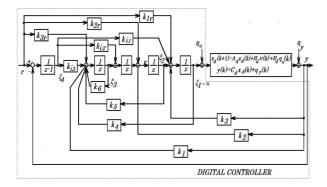

The DC-DC converter as shown in Fig.1 has been manufactured. In order to realize the approximate 2DOF digital controller which satisfies given specifications, we use the DSP(TI TMS320LF2801). This DSP has a builtin AD converter and a PWM switching signal generating part. The triangular wave carrier is adopted for the PWM switching signal. The switching frequency is set at  $400[\mathrm{KHz}]$  and the peakto-peak amplitude  $C_m$  is  $125[\mathrm{V}]$ . The LC circuit is a filter for removing carrier and switching noises. where

Manuscript received on December 19, 2008; revised on April 20, 2009.

<sup>1,3,4</sup> The authors are with Dept. of Electronic Engineering, The University of Electro-Communications, 1-5-1 Chofu-ga-oka, Chofu, Tokyo 182-8585, Japan., E-mail: higuchi@ee.uec.ac.jp, nakano@ee.uec.ac.jp, ka-jikawa@ee.uec.ac.jp

<sup>2.5</sup> The authors are with TDK-LAMBDA K.K., 2701 Togawa, Settaya, Nagaoka 940-1195, Japan., E-mail: e.takegami@jp.tdk-lambda.com, s.tomioka@jp.tdk-lambda.com

<sup>&</sup>lt;sup>6</sup> The author is with 6King Mongkuts University of Technology Thonburi, 126 Pracha-utid Road Bangmod, Toongkru, Bangkok, Thailand., E-mail: kosin.cha@gmail.com

Fig.1: DC-DC converter

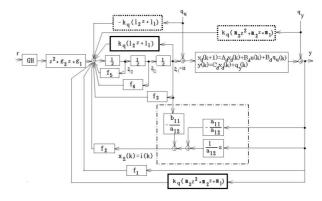

Fig.2: Controlled object with 3 input delay elements

$C_0$  is  $300[\mu\mathrm{F}]$  and  $L_0$  is  $0.46[\mu\mathrm{H}]$ . If the frequency of control signal u is smaller enough than that of the carrier, the state equation of the DC-DC converter at a resistive load in Fig.1 except the controller in DSP can be expressed from the state equalizing method[14] as follows:

$$\begin{cases} \dot{x} = A_c x + B_c u + B_c q_u \\ y = C_x + q_y \end{cases} \tag{1}$$

where

$$x = \begin{bmatrix} e_0 \\ i \end{bmatrix} A_c = \begin{bmatrix} -\frac{1}{C_0 R_L} & \frac{1}{C_0} \\ -\frac{1}{L_0} & -\frac{R_1}{L_0} \end{bmatrix} B_c = \begin{bmatrix} 0 \\ \frac{k_p}{L_0} \end{bmatrix}$$

$$c = [1 \ 0] \ u = e_i \ y = e_0 \ k_p = -\frac{V_i N_2}{C_m N_1}$$

and  $R_0$  is the total resistance of coil and ON resistance of FET, etc., whose value is  $0.015[\Omega]$ . Then the discrete-time state equation of the system (1) with a zero-order hold is expressed as

$$\begin{cases} x_d(k+1) = A_d x_d(k) + B_d u(k) + B_d q_u(k) \\ y_k = C x_d(k) + q_y(k) \end{cases}$$

(2)

where

$$A_d = \begin{bmatrix} a_{11} & a_{12} \\ a_{21} & a_{22} \end{bmatrix} = e^{A_c T}, B_d = \begin{bmatrix} b_{11} \\ b_{21} \end{bmatrix} = \int_0^T e^{A_c \tau} B_c d_{\tau}$$

The transfer function of the system (2) is as follows:

$$G_p(z) = \frac{N_p(z)}{D_n(z)} \tag{3}$$

where

$$N_p(z) = b_{11}z + b_{21}a_{12} - a_{22}b_{11}$$

**Fig.3:** Feedforward from equivalent disturbances  $q_u$  and  $q_y$ , and model matching with state feedback

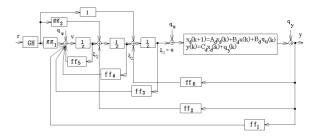

Fig.4: Model matching system using only voltage (output) feedback

$$D_p(z) = z^2 - (a_{11} + a_{22})z + a_{11}a_{22} - a_{21}a_{12}$$

For practical use of DC-DC converters, the characteristics of startup transient response, dynamic load responses and output responses at sudden input voltage changes are important. The DC-DC converter with the following specifications 1-7 is designed and manufactured:

- 1. Input voltage  $V_i$  is 48[V] and output voltage  $e_o$  is 3.3[V].

- 2. Startup transient responses are almost the same at resistive load and parallel load of resistance and capacity, where  $0.16 \leq R_L < \infty[\Omega]$  and  $0 \leq C_L \leq 300[\mu \mathrm{F}]$ .

- 3. The rising time of the startup transient response is smaller than  $100[\mu s]$ .

- 4. Against all the loads of spec.1, an over-shoot is not allowable in the startup transient response.

- 5. The dynamic load response is smaller than 25[mV] against 10[A] change of load current.

- 6. The specs. 2, 3, 4 and 5 are satisfied also to change of input voltage of  $\pm 20\%$ .

- 7. Regulation of output voltage is smaller than 25 [mV] at the sudden change of input voltage within  $\pm 20\%$ .

Specs 2, 5 and 7 are new ones. These specs are more severe than  $200[\mu\text{F}]$  and 50[mV] in references[11]. The load changes for the controlled object

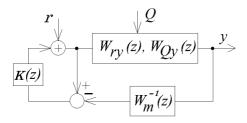

Fig.5: System reconstituted with inverse system and filter

Fig. 6: Approximate 2DOF digital integral type con $trol\ system$

and the input voltage change are considered as parameter changes in eq.(1). Such parameter changes can be transformed to equivalent disturbances  $q_u$  and  $q_u$  as shown in **Fig.2** and **Fig.3**[15] even in discretetime systems. Therefore, what is necessary is just to constitute the control systems whose pulse transfer functions from equivalent disturbances  $q_u$  and  $q_y$ to the output y become as small as possible in their amplitudes, in order to robustize or suppress the influence of these parameter changes and input voltage changes.

## 2. DESIGN METHOD FOR APPROXI-MATE 2DOF DIGITAL CONTROLLER WITH ADDITIONAL ZEROS

#### A. Addtional zeros method

The following equation is obtained by repeating the difference of the output of eq.(2):

$$Y = O^*xd(k) + U\bar{u}(k) + U\bar{q}_u + \bar{q}_u \tag{4}$$

where

$$Y = \begin{bmatrix} y(k) \\ y(k+1) \\ y(k+2) \end{bmatrix} O^* = \begin{bmatrix} C \\ CA_d \\ CA_d^2 \\ CA_d^2 \end{bmatrix} U = \begin{bmatrix} 0 & 0 \\ CB_d & 0 \\ CA_dB_d & CB_d \end{bmatrix} \qquad B_{dw} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 1 \end{bmatrix} C_{dw} = \begin{bmatrix} C & 0 & 0 & 0 \end{bmatrix} \xi_1(k) = u(k)$$

$$\bar{u} = \begin{bmatrix} u(k) \\ u(k+1) \end{bmatrix} \bar{q}_u = \begin{bmatrix} q_u(k) \\ q_u(k+1) \end{bmatrix} \bar{q}_y = \begin{bmatrix} q_y(k) \\ q_y(k+1) \\ q_y(k+1) \end{bmatrix}$$

If both sides of eq.(4) are mulutiplied by  $\bar{I}_2$  from the left,  $x_d$  is obtained by the following equation:

$$x_d(k) = (\bar{I}_2 O^*)^{-1} \bar{I}_2 Y - (\bar{I}_2 O^*)^{-1} \bar{I}_2 U \bar{u}(k) - (\bar{I}_2 O^*)^{-1} \bar{I}_2 U \bar{q}_u - (\bar{I}_2 O^*)^{-1} \bar{I}_2 \bar{q}y$$

(5)

where

$$\bar{I}_2 = \left[ \begin{array}{ccc} 1 & 0 & 0 \\ 0 & 1 & 0 \end{array} \right]$$

By substituting the above equation into eq.(4), the following equation is obtained:

$$(I_3 - O^*(\bar{I}_2O^*)^{-1}\bar{I}_2)U\bar{q}_u + (I_3 - O^*(\bar{I}_2O^*)^{-1}\bar{I}_2)\bar{q}_y$$

=  $(I_3 - O^*(\bar{I}_2O^*)^{-1}\bar{I}_2)Y - (I_3 - O^*(\bar{I}_2O^*)^{-1}\bar{I}_2)U\bar{u}$  (6)

where I3 is a  $3 \times 3$  unit matrix. That is,  $\bar{q}_u$  and  $\bar{q}_y$  can be replaceded to Y and  $\bar{u}(k)$ . Eq.(6) is transformed as

$$- (l_2z + l_1)q_u(k) + (z^2 + m_2z + m_1)q_y(k)$$

=  $(l_2z + l_1)u(k) + (z^2 + m_2z + m_1)y(k)$  (7)

where

$$\begin{bmatrix} l_1 & l_2 \end{bmatrix} = -(I_3 - O^*(\bar{I}_2 O^*)^{-1} \bar{I}_2) U$$

$$\begin{bmatrix} m_1 & m_2 & m_3 \end{bmatrix} = (I_3 - O^*(\bar{I}_2 O^*)^{-1} \bar{I}_2)$$

(8)

The system as depicted in Fig.2 is constituted in consideration of a delay time for AD conversion time etc., replacing current feedback and zeros addition. The state equation in Fig.2 can be expressed as

$$\begin{cases} x_{dw}(k+1) = A_{dw}x_{dw}(k) + B_{dw}v(k) \\ y(k) = C_{dw}x_{dw}(k) \end{cases}$$

(9)

where

$$x_{dw}(k) = \begin{bmatrix} x_d(k) \\ \xi_1(k) \\ \xi_2(k) \\ \xi_3(k) \end{bmatrix} A_{dw} = \begin{bmatrix} A_d & B_d & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 \end{bmatrix}$$

$$B_{dw} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 1 \end{bmatrix} C_{dw} = \begin{bmatrix} C & 0 & 0 & 0 \end{bmatrix} \xi_1(k) = u(k)$$

Applying the following feedforwards from  $q_u$ ,  $q_y$  and r, and state feedback from xdw for model matching to the system in eq.(9), the system shown in Fig.3 is

$$\begin{split} v(k) = -k_g(l_2z + l_1)q_u(k) + k_q(z^2 + m_2z + m_1)q_y(k) \\ + (z^2 + g_2z + g_1)r(k) + [f_1 \ f_2 \ f_3 \ f_4 \ f_5 \ f_6] \ x_dw(k) \ (10) \end{split}$$

In Fig.3, the parts surrounded by dotted lines are the feedforward coefficients from  $q_u$  and  $q_y$  and the part surrounded by a chain line is the estimated part of current. From eq.(7), the feedforwards of eq.(10) are changed as

$$v(k) = k_q(l_2z + l_1)u(k) + k_q(z^2 + m_2Z + m_1)q_y(k) + (z^2 + g_2z + g_1)r(k) + [f_1 \ f_2 \ f_3 \ f_4 \ f_5 \ f_6]x_{dw}(k)(11) \text{ where}$$

That is, the parts surrounded by the dotted lines are replaced by the parts surrounded by solid lines from u and y. The system except the parts surrounded by the dotted lines in Fig.3 can be transformed equivalently as shown in **Fig.4**. In Fig.4,

$$ff_{1} = f_{1} - f_{2}(a_{11}/a_{12}) + k_{q}m_{1} + f_{5}(k_{q}m_{2} + f_{2}/a_{12})$$

$$+ f_{5}^{2}k_{q}m_{3} + (f_{4} + k_{q}l_{2})k_{q}m_{3}$$

$$ff_{2} = k_{q}m_{2} + f_{2}/a_{12} + f_{5}k_{q}m_{3}$$

$$ff_{3} = f_{3} - f_{2}(b_{11}/a_{12}) + k_{q}l_{1}$$

$$ff_{4} = f_{4} + k_{q}l_{2}$$

$$ff_{5} = f_{5}$$

$$ff_{6} = k_{q}m_{3}$$

(12)

The transfer functions between r and y,  $q_u$  and y, and  $q_y$  and y in Fig.4 are described as

$$W_{ry}(z) = N_{ry}(z)/D(z) \tag{13}$$

$$W_{q_u y}(z) = N_{q_u y}(z)/D(z) \tag{14}$$

$$WW_{q_u y}(z) = N_{q_u y}(z)/D(z)$$

(15)

where

$$\begin{split} N_{ry}(z) &= GH(z^2 + g_1z + g_0)(b_{11}z + b_{21}a_{12} - a_{22}b_{11}) \\ N_{q_uy}(z) &= N_{qz}N_p \\ N_{q_uy}(z) &= N_{qz}D_p \\ N_{qz} &= (a_{12}z^3 - a_{12}f_5z^2 + (a_{12}b_{11}k_q - a_{12}b_{11})z \\ &- f_3a_{12} - f_2b_{11} - a_{12}a_{22}b_{11}k_q - a_{12}^2b_{21}k_q) \\ D(z) &= z^5 + (-f_5 - a_{22} - a_{11})z^4 + (a_{11}f_5 \\ &+ a_{11}a_{22} - a_{21}a_{12} + a_{22}f_5 - f_4)z^3 \\ &+ (a_{21}a_{12}f_5 - f_3 + a_{11}f_4 - a_{11}a_{22}f_5 \\ &+ a_{22}2f_4)z^2 + (a_{22}f_3 + a_{21}a_{12}f_4 + a_{11}f_3 \\ &- b_{11}f_1 - f_2b_{21} - a_{11}a_{22}f_4)z + f_2a_{11}b_{21} \\ &- a_{21}f_2b_{11} + a_{21}a_{12}f_3 + f_1a_{22}b_{11} \\ &- f_1a_{12}b_{21} - a_{11}a_{22}f_3 \end{split}$$

From D(z), the poles of the overall system can be arranged arbitrarily by  $f_1, f_2, f_3, f_4$  and  $f_5$ . From  $N_{ry}(z)$ , two zeros of r-y can be arranged arbitrarily by g0 and g1. Moreover, from common  $N_{qz}$  in  $N_{qz}$ (s) and  $N_{q_yy}(s)$ , one zeros of  $q_u$ -y and  $q_y$  - y can be arranged arbitrarily at the same place by  $k_q$ . That is, one zeros can be added arbitrarily to  $W_{Q_n}$ . B. Design method

First, the transfer function between the reference input r and the output y is specified as

$$W_{ry}(z) = N_H(z)/D_H(z) \tag{16}$$

$$N_H(z) = (1 + H_1)(1 + H_2(1 + H_3)(z - n_1)(z - n_2)$$

$$\times (z + H_4)(z + H_5)$$

$$D_H(z) = (1 - n_1)(1 - n_2)(z + H_1)(z + H_2)(z + H_3)$$

$$\times (z + H_4)(z + H_5)$$

$n_1$  and  $n_2$  are the zeros for the discrete-time controlled object (2).  $[f_1f_2f_3f_4f_5]$ ,  $[g_1g_2]$  and GH are determined so that  $W_{ry}(z)$  becomes eq.(16). And the transfer function among the disturbance inputs  $q_u, q_y$ and the output y is specified as

$$W_{q_u y}(z) = (z-1)\bar{N}_{qz}N_p/D_H(z)$$

(17)

$$W_{q_n y}(z) = (z-1)\bar{N}_{qz}D_p/D_H(z)$$

(18)

Here the zeros are placed at 1 by setting  $k_q$  as the solution of  $N_{qz}(1) = 0$ . The parameter  $k_q$  becomes as follows:

$$k_q = \frac{-a_{12} + a_{12}f_5 + a_{12}f_4 + f_3a_{12} - f_2b_{11}}{a_{12}(b_{11} - a_{22}b_{11} + b_{21}a_{12})}$$

(19)

$\bar{N}_{qz}$  is the remaining zeros of  $N_{qz}$  which cannot be placed arbitrarily.

It shall be specified that the relation of  $H_1$  and  $H_2, H_3 \text{ becomes } |H_1| \gg |Re(H_2)|, |H_1| \gg |Re(H_3)|.$ Then  $W_{ry}(z)$  can be approximated to the following first-order model:

$$W_{ry}(z) \approx W_m(z) = \frac{1 + H_1}{z + H_1}$$

(20)

This target characteristics  $W_{ry}(z) \approx W_m(z)$  is specified so as to satisfy the specs.3 and 4.

The system added the inverse system and the filter to the system in Fig.4 is constituted as shown in **Fig.5**. In Fig.5, the transfer function K(z) becomes

$$K_z = \frac{k_z}{z - 1 + k_z} \tag{21}$$

The transfer functions between r-y,  $q_u-y$  and  $q_y-y$ of the system in Fig.5 are given by

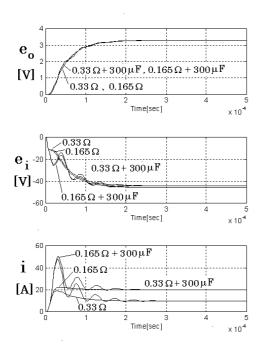

Fig. 7: Simulation results of the startup responses at various loads

*Fig.8*: Simulation result of the dynamic load response at resistive load

$$y = \frac{1+H_1}{z+H_1} \frac{z-1+k_z}{z-1+k_zW_s(z)} W_s(z) r$$

(22)

$$y = \frac{(z-1)^2}{z-1+k_2} \frac{z-1+k_z}{z-1+k_zW_s(z)} \frac{\bar{N}_{qz}N_p}{D_H(z)} q_u(23)$$

$$y = \frac{(z-1)^2}{z-1+k_2} \frac{z-1+k_z}{z-1+k_zW_s(z)} \frac{\bar{N}_{qz}D_p}{D_H(z)} q_u(24)$$

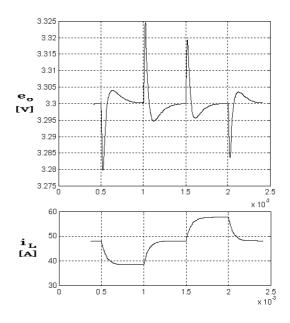

Simulation result of the output response at resistive load when the input voltage changing suddenly

Fig. 10: The manufactured new quarter brick DC-DC converter

where

$$W_s(z) = \frac{(1+H_2)(1+H_3)(z-n_1)(z-n_2)}{(z+H_2)(z+H_3)(1-n_1)(1-n_2)}$$

(25)

Here, if  $W_s(z) \approx 1$ , then eqs.(22), (23) and (24) become, respectively,

$$y \approx \frac{1+H_1}{z+H_1}r \tag{26}$$

$$y \approx \frac{(z-1)^2}{z-1+k_z} \frac{\bar{N}_{qz} N_p}{D_H(z)} q_u \tag{27}$$

$$y \approx \frac{1 + H_1}{z + H_1} r$$

$$y \approx \frac{(z - 1)^2}{z - 1 + k_z} \frac{\bar{N}_{qz} N_p}{D_H(z)} q_u$$

$$y \approx \frac{(z - 1)^2}{z - 1 + k_z} \frac{\bar{N}_{qz} D_p}{D_H(z)} q_y$$

(28)

From eqs.(26), (27) and (28), it turns out that the characteristics from r to y can be specified with  $H_1$ , and the characteristics from  $q_u$  and  $q_y$  to y can be

independently specified with  $k_z$ . That is, the system in Fig.5 is an approximate 2DOF, and its sensitivity against disturbances becomes lower with the increase of  $k_z$ .

If an equivalent conversion of the controller in Fig.5 is carried out, the approximate 2DOF digital integral-type control systems will be obtained as shown in **Fig.6**. In Fig.6, the parameters of the controller are as follows:

$$k_{1} = (f_{1} - f_{2}a_{11}/a_{12} + k_{q}(-a_{11}^{2} - a_{21}a_{12} + a_{12}a_{11} + a_{12}a_{22})a_{11}/a_{12} + f_{5}(-k_{q}(a_{12}a_{11} + a_{12}a_{22})/a_{12} + f_{2}/a_{12}) + f_{5}^{2}k_{q} + (f_{4} - k_{q}b_{11})k) - GHk_{z}(g_{0} + (g_{1} + f_{5})f_{5} + f_{4} - k_{q}b_{11})/(1 + H2)$$

$$k_{2} = k_{q} - GHk_{z}/(1 + H2)$$

$$k_{3} = -k_{q}(a_{11}a_{12} + a_{12}a_{22})/a_{12} + f_{2}/a_{12} + f_{5}k_{q} - (g_{1} + f_{5})GHk_{z}/(1 + H2)$$

$$k_{4} = f_{3} - f_{2}b_{11}/a_{12} + k_{q}((a_{12}a_{11} + a_{12}a_{22})b_{11}/a_{12} - a_{11}b_{11} - b_{21}a_{12})$$

$$k_{5} = f_{4} - k_{q}b_{11}$$

$$k_{6} = f_{5}$$

$$k_{i}1 = (g_{0} + (g_{1} + f_{5})f_{5} + f_{4} - k_{q}b_{11})GHk_{z}$$

$$k_{i}2 = (g_{1} + f_{5})GHk_{z}$$

$$k_{i}3 = GHk_{z}$$

$$k_{1}r = GH$$

$$k_{2}r = (g_{1} + f_{5})GH$$

$$k_{3}r = (g_{0} + (g_{1} + f_{5})f_{5} + f_{4} - k_{b11})GH$$

$$(29)$$

## 3. EXPERIMENTAL STUDIES

The sampling period T are set at  $2.5[\mu s]$ . The nominal value of  $R_L$  is  $0.33[\Omega]$ . We design a control system so that all the specifications are satisfied. First of all, in order to satisfy the specification on the rising time of the startup transient response,  $H_1$ ,  $H_2$ ,  $H_3$ ,  $H_4$  and  $H_5$  are specified as

$$H_1 = -0.94H_2 = -0.18 + 0.2iH_3 = -0.18 - 0.2i$$

$H_4 = -0.2 + 0.3iH_5 = -0.2 - 0.3i$  (30)

Then from eq.(19),  $k_q = 548.31$ . After that,  $k_z$  is set up with  $k_z = 0.17$ . Then the parameters of controller become as follows:

$$k_1 = 861.86$$

$k_2 = 584.67$   $k_3 = -1061.2$

$k_4 = 0.72688$   $k_5 = 0.45193$   $k_6 = -0.178811$

$k_{i1} = -1.4955$   $k_{i2} = 1.2629$   $k_{i3} = -2.1818(31)$

It must be better that  $k_{r1}$  and  $k_{r2}$  are set to 0, since the characteristics of the control system hardly changes in this case.

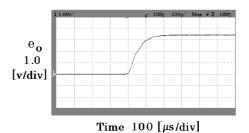

**Fig.11:** Experimental result of the startup response at resistive load  $(R_L = 0.33 |\Omega|)$

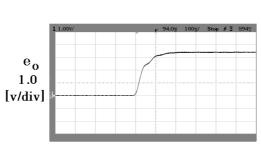

Fig. 12: Experimental result of the startup response at resistive load  $(R_L = 0.165 [\Omega])$

The simulation results of the startup responses are shown in **Fig.7**. From the output voltage  $y = e_0$  in this figure, it turns out that the specifications are satisfied. It is checked that almost the same simulation results as in Fig.7 are obtained when the input voltage Vi is changed by  $\pm 20\%$ . The simulation result of the dynamic load responses is shown in Fig.8. Fig.8 shows the result at resistive load whose value is changed as  $R_L = 0.33 \leftrightarrow 0.165 [\Omega]$ . It is checked that almost the same simulation result as in Fig.8 is obtained at parallel load of resistance ( $RL = 0.33 \rightarrow$  $0.165[\Omega]$ ) and capacity ( $CL = 300[\mu F]$ ). Fig.9 shows the output response at resistive load  $R_L = 0.33[\Omega]$ when input voltage changed suddenly as  $48 \rightarrow 38 \rightarrow$  $48 \rightarrow 58 \rightarrow 48[V]$ . It turns out that all the specifications are satisfied.

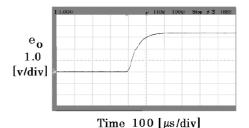

Time 100 [µs/div]

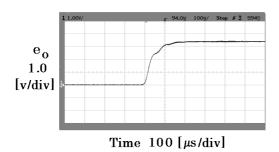

**Fig. 13:** Experimental result of the startup response at parallel load of resistance  $(R_L = 0.33[\Omega])$  and capacity  $(C_L = 300[\mu F])$

Fig.14: Experimental result of the startup response at resistive load  $(R_L = 0.33[\Omega], C_L = 300[\mu F])$  when the input voltage is 58[V]

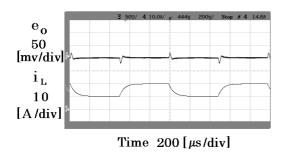

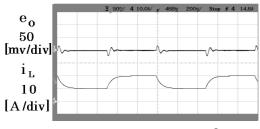

Fig.15: Experimental result of the dynamic load response at resistive load  $(RL = 0.33 \leftrightarrow 0.165[\Omega])$

The manufactured, new DC-DC converter builtin DSP is shown in Fig.10. This fits in a quarter brick size  $(37\text{mm} \times 58\text{mm} \times 8\text{mm})$  one. Experimental results when the digital controller with the parameters of eq.(31) is equipped in the DSP shown in **Figs.11-18**. Fig.11 shows the startup response at the resistive load  $R_L = 0.33[\Omega]$ . Fig.12 shows the startup response at the resistive load  $R_L = 0.165[\Omega]$ . Fig.13 shows the startup response at parallel load of resistance  $R_L = 0.33[\Omega]$  and capacity  $CL = 300[\mu F]$ . From y = eo in these figures, it turns out that almost the same experimental results as the simulation ones in Fig.7 are obtained and the specifications are satis fied. Fig. 14 shows the startup response when the input voltage  $V_i$  is 58[V]. It is checked that the specifications are satisfied when the input voltage Vi is

Time 200 [ $\mu$ s/div]

**Fig.16:** Experimental result of the dynamic load response at resistive load  $(R_L = 0.33 \leftrightarrow 0.165[\Omega], C_L = 300[\mu F])$

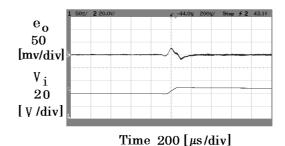

Fig.17: Experimental result of the output repones at parallel load of resistance  $(R_L = 0.33[\Omega])$  and capacity  $(C_L = 300[\mu F])$  when input voltage changing suddenly from 38/V to 48/V

Time 200 [ $\mu$ s/div]

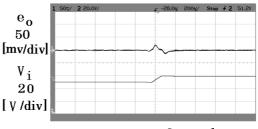

Fig. 18: Experimental result of the output repones at parallel load of resistance ( $R_L = 0.33[\Omega]$ ) and capacity ( $CL = 300[\mu F]$ ) when input voltage changing suddenly from 48[V] to 58[V]

changed by 20%. Fig.15 shows the dynamic load response at resistive load  $(RL = 0.33 \leftrightarrow 0.165[\Omega])$ . Fig.16 shows the dynamic load response at the parallel load of resistance  $(RL = 0.33 \leftrightarrow 0.165[\Omega])$  and capacity ( $CL = 300[\mu F]$ ). It turns out that almost the same experimental results as the simulation ones in Fig.8 are obtained. Although the load current changed suddenly from 20 [A] to 10 [A], and vice versa, the output voltage change is very small and is suppressed within about 25[mV]. Fig.17 shows the output response at parallel load of resistance ( $R_L$  =  $0.33[\Omega]$ ) and capacity  $(C_L = 300[\mu F])$  when input voltage changed suddenly from 38[V] to 48[V]. Fig.18 shows the output response at parallel load of resistance  $(RL = 0.33[\Omega])$  and capacity  $(C_L = 300[\mu F])$ when the input voltage changed suddenly from 48[V] to 58[V]. It turns out that almost the same experimental results as the simulation ones in Fig.9 are obtained. It is checked that almost the same experimental results as Fig.9 are obtained when the input voltage changed suddenly from 48[V] to 58[V]. It turns out that the specifications are satisfied. We checked by experiments that all other specifications are satisfied.

#### 4. CONCLUSIONS

In this paper, the concept of controller of DC-DC converters to attain good robustness against extensive load changes and input voltage changes was given. The proposed digital controller was implemented on the DSP(TI TMS320LF2801). The new DC-DC converter built-in this DSP was manufactured. It was shown from experiments that the sufficiently robust digital controller is realizable. The characteristics of the dynamic load responses and the output responses against sudden input voltage changes were improved by using our proposed method for approximate 2DOF digital controller with additional zeros. This fact demonstrates the usefulness and practicality of our method. The future work is to design a digital controller robust enough, when (LC+LC) circuits etc. are used as filters for removal of switching and carrier noises.

#### References

- L. Guo, J. Y. Hung, and R. M. Nelms, "Digital controller Design for Buck and Boost Converters Using Root Locus," *IEEE IECON2003*, 1864/1869 (2003).

- [2] H. Guo, Y. Shiroishi and O. Ichinokura, "Digital PI Controller for High Frequency Switching DC/DC Converters Based on FPGA," *IEEE INTELECO3*, 536/541 (2003).

- [3] G. Papafotiou and N. Margaris, "H ∞ discrete time control for the buck DC-DC converter," *IEEE IECON'2002*, Vol. 54, No.3, 55/61(2002).

- [4] Yuk-Ming Lai, Siew-Chong Tan, and Chi-Kin Wu, "Design of a PWM Based Sliding Mode Controlled Buck-Boost Converter in Continuous-Conduction-Mode," ECTI Trans. on EEC, Vol. 5, No.1, 1528/1536(2007).

- [5] Kuo-Hsiang Cheng, Chun-Fei Hsu, Chih-Min Lin, Tsu-Tian Lee, and Chunshien Li, "Fuzzy-Neural Sliding-Mode Control for DCDC Converters Using Asymmetric Gaussian Membership Functions," *IEEE Trans. on Industrial Electron*ics, Vol. 54, No.3, 1528/1536(2007).

- [6] L. Corradini, P. Mattavelli and D. Maksimovic, "Robust Relay- Feedback Based Autotuning for DC-DC Converters," *IEEE PESC2008*, 2196/2202(2007).

- [7] Yu Ni, Jianping Xu. "Study of Global Sliding Mode Controlled Switching DC-DC Converters," *IEEE ICIT2008*, 21/24(2008).

- [8] K. Higuchi, K. Nakano, T.Kajikawa, E.Takegami, S.Tomioka, K.Watanabe, "Robust Control of DC-DC Converter by High-Order Approximate 2-Degree-of-Freedom Digital Controller," *IEEE IECON2004*, (CD-ROM), 2004.

- [9] E. Takegami, K. Higuchi, K. Nakano, K. Watanabe, S. Tomioka, "The Metohd for Determining Parameters of Approximate 2DOF Digital Con-

- troller for Robust Control of DC-DC Converter," *ECTI-CON2005*, pp.593-596, 2005.

- [10] K. Higuchi, E. Takegami, K. Nakano, K Watanabe, S. Tomioka, "NEW DESIGN OF RO-BUST DIGITAL CONTROLLER FOR DV-DC CONVERTERS," IFAC 16th Triennial World Congress (CD-ROM), 2005.

- [11] E. Takegami, K. Higuchi, K. Nakano, S. Tomioka and K. Watanabe, "The Method for Determining Parameters of Approximate 2DOF Digital Controller for Robust Control of DC-DC Converter," Trans. on Electrical Eng. Electronics, and Communications, Vol.4, No.1, pp.13-21 (2006.2).

- [12] E. Takegami, K. Higuchi, K. Nakano and S. Tomioka, "Appoximate 2DOF Digital Control for DC-DC Converter with additional Zeros," ECTI-CON2007, pp.321-324, 2007.

- [13] E. TAKEGAMI, K. HIGUCHI, K. NAKANO, T. Kajikawa, "Digital Robust Control for DC-DC Converter with Second-Order Differential Characteristics," *IEEE IECON2007*, pp.1999-2004, 2007.

- [14] H. Fukuda and M. Nakaoka, "State-Vector Feedback Controlledbased 100kHz Carrier PWM Power Conditioning Amplifier and Its High-Precision Current-Tracking Scheme," IEEE IECON93, pp. 1105/1110(1993).

- [15] R.Tagawa, "Definition and Application of New Equivalent Distubances," Prep. of The 15th Dyamical System Theory Symposium, pp.37-42, 1992(in Japanese).

Kohji Higuchi recieved Dr. Eng. degree from Hokkaido University, Sapporo, Japan in 1981. From 1980 he was a Research Associate at the University of Electro-Communications. From 1982 he was an Assistant Professor at the University of Electro-Communications Fukuoka. He is currently an Associate Professor in the Department of Electronic Engineering, the University of Electro-Communications, Tokyo, Japan.

His interests include Power Electronics and Control Engineering. He is a member of IEEE, IEICE, IEEJ and the Society of Instrument and Control Engineers (SICE).

Eiji Takegami received Dr. Eng. degree the University of Electro-Communications, Tokyo, Japan in 2008. From 1997 he was a Engineer, Development and Design of switching power supply at Nippon Electric Industry Co., Ltd.(present: TDK-LAMBDA K.K.).He is a member of IEEE, IEICE, and the Society of Instrument and Control Engineers (SICE).

Kazushi Nakano recieved Dr. Eng. degree from Kyushu University, Fukuoka, Japan in 1982. From 1980 he was a Research Associate at Kyushu University. From 1986 he was an Associate Professor at Fukuoka Institute of Technology. He is currently a Professor in the Department of Electronic Engineering, the University of Electro-Communications, Tokyo, Japan. His interests include system identification/control and their ap-

plications. He is a member of IEEE, IEICE, IEEJ and the Society of Instrument and Control Engineers (SICE).

Tatsuyoshi Kajikawa received B. Eng. Degree from Tokyo University of Science, Tokyo, Japan in 1990. From 1983 he was a Engineering staff in the Department of Electronic Engineering, the University of Electro-Communications, Tokyo, Japan. He is currently a Tcchnical Official in the Department of Electro-Communications, Tokyo, Japan. His interests include

Power Electronics and Control Engineering. He is a member of IEEJ.

Satoshi Tomioka received B. Eng. degree from Tokyo Denki University, Tokyo, Japan in 1984. From 1984 he is a Engineer, Development and Design of Switching Power Supply at NEMIC-LAMBDA Ltd.(present: TDK-LAMBDA K.K.).

Kosin Chamnongthai currently works as associate professor at Electronic and Telecommunication Engineering Department, Faculty of Engineering, King Mongkut's University of Technology (KMUTT), and also serves as associate editor of ECTI-EEC Trans. He has recieved B.Eng. in Applied Electronic Engineering from the University of Electrocommunication (UEC), Tokyo in 1985, M.Eng. in Electrical Engineering from

Nippon Institute of Technology (NIT), Saitama in 1987 and D.Eng. in Electrical Engineering from Keio University, Tokyo Japan in 1991. His research interests include image processing, computer vision, robot vision, and natural language processing. He is a member of IEEE, IPS, TRS, IEICE, TESA and ECTI.