# Geometrical Variation of a Conductive Filament in RRAM and Its Impact on a Single-Event Upset

Vijay H. M.<sup>†</sup> and V. N. Ramakrishnan, Non-members

## **ABSTRACT**

Resistive random access memory (RRAM) is a promising candidate for industry and academia from the research and development perspective. The resistance of RRAM depends on the geometrical dimensions, growth, and rupture of the conductive filament. In this work, the geometrical dimensions such as the length and width of the filament are varied to analyze the resistance. Moreover, the RRAM can be used in aerospace applications. Therefore, the impact of a single-event upset on resistance of RRAM is investigated by means of a double exponential current pulse. The performance of the device is compared in terms of resistance before and after irradiation. A decrease in its original resistance has been observed after radiation.

**Keywords**: Conductive Filament, Single-Event Upset, SEU, Resistive Random Access Memory, RRAM

# 1. INTRODUCTION

In the present and future world, the interaction between people and devices is likely to increase, potentially reaching approximately 4,800 times per day. Hence, data will be acquired from sensors and processed, which requires fast and voluminous data storage as well as real-time processing [1]. To accelerate the processing, emerging memory devices and technologies are promising candidates for non-volatile, low-power, high-speed, low-cost handling of big data [2]. The MRAM, FRAM, Nano-RAM, Racetrack, and RRAM are strong candidates from the family of memory devices Resistive switching memories are the leading solution for neuromorphic computing and upcoming storage systems [4]. The growth and rupture of the conductive filament modulate the RRAM's effectiveness. The formation and rupture of the conductive filament leads to a low-resistance state (LRS) and a high-resistance state (HRS), respectively [5].

Many researchers have extensively investigated the formation and shape of the nano conductive filaments

in the switching layer. Two main types of nano filaments are mainly observed in RRAM: oxygen vacancy nano and metal nano. Metal filaments are observed in RRAM systems like Ag/GeS<sub>2</sub>/W [6], Ag/AgI/Pt [7], Ag/Ta<sub>2</sub>O<sub>5</sub>/Pt [8], and Nb/ZnO/Pt [9]. Oxygen vacancy nano filament RRAM devices consist of Pt/HfO2/Pt [10],  $W/CeO_x/SiO_2/NiSi_2$  [11], and  $Ti/TiO_2/SrTiO_3/n + Si$  [12]. The metal filaments are more distinct than the oxygen vacancy filaments [13]. In the switching layer, the lack of uniformity in the formation of nano conductive filaments leads to instability in the RRAM switching performance [14-15]. Many approaches have been proposed to overcome the aforementioned problem such as employing bilayer structures [16-17], the placement of pyramid-shaped electrodes [18-19], implanting metal nano particles in the switching/insulating layer [20-22], and doping the switching layer [23–24]. Celano et al. [25] visualized three-dimensional conductive nano filaments. They employed an approach known as conductive atomic force microscopy (CAFM) to acquire information on the nano filaments, observing conical-shaped filaments and noting that the narrow end of the filament was nearer to the inert electrode. While Wu et al. [26] observed the formation of single as well as multiple nano filaments in the dielectric stack of Ni/HfO<sub>2</sub>/SiO<sub>x</sub>/Si RRAM device. In the case of multiple filaments, there is a large variation in the size of the nano filaments. The shape of the filament is in the form of truncated cones. In practice, the compliance current controls the growth of the conductive nano filament [27]. However, all the research referred to concentrates on controlling the nano filaments and their number but this work mainly focuses on the variation in geometrical dimensions of the nano filament to acquire RRAM resistance.

In this work, Section 2 deals with a single-event upset in RRAM. The simulation setup is described in Section 3 while Section 4 focuses on the results and discussion. The conclusion is presented in Section 5.

# 2. EFFECT OF A SINGLE-EVENT UPSET ON RRAM

The ionizing particles passing through the semiconductor memories induce soft errors or a single-event upset (SEU) [28]. These ionizing particles sometimes cause hard errors too. This is termed a single-event latch-up (SEL) [29]. The damage caused is temporary in the case of soft errors but permanent for hard errors. A reliability problem arises in the memories due to the influence of an SEU [30]. The factors governing the SEU in memories are the sensitive region of the device and

Manuscript received on June 26, 2021; revised on August 26, 2021; accepted on September 13, 2021. This paper was recommended by Associate Editor Kriangkrai Sooksood.

The authors are with the School of Electronics Engineering, Vellore Institute of Technology, Vellore, India.

<sup>&</sup>lt;sup>†</sup>Corresponding author: vijayh.m2016@vitstudent.ac.in

<sup>©2022</sup> Author(s). This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 4.0 License. To view a copy of this license visit: https://creativecommons.org/licenses/by-nc-nd/4.0/.

Digital Object Identifier: 10.37936/ecti-eec.2022201.246101

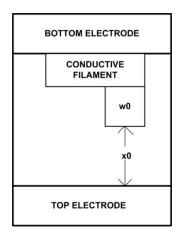

Fig. 1: Structure of the RRAM.

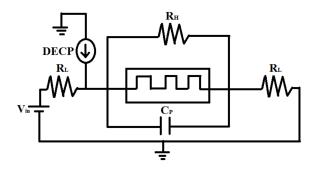

Fig. 2: Circuit setup for the simulation [37].

minimum ionization energy. The linear energy transfer (LET) and the critical charge ( $Q_C$ ) are the parameters which assist threshold measurement [31]. The x-rays, heavy ions, particle accelerators, Cobalt-60, cyclotron, alpha particles, and gamma rays can be bombarded to study the SEU impact on memory devices [32].

Liu et al. [33] considered the 1T1R and the crossbar array in the investigation of single as well as multi-bit upsets. The susceptibility analysis is performed by means of simulations at the circuit level. In this work, it is evident that the maximum radiation tolerance is demonstrated by the crossbar array. The sensitive nodes are the driver circuits. Bennett et al. [34] employed TCAD for the modeling, incorporating the 1T1R array. The changes are induced in the array by modeling the irradiation. Changes in the RRAM performance can be observed to have an exponential relationship with the potential applied across the device. proposed that the radiation hardened the RRAM in space applications. Liu et al. [35] considered both the crossbar and 1T1R array for irradiation due to the heavy ions involved. The rate of upset, vulnerable time window, and the sensitive region are the factors imbibed in the susceptibility analysis. The minimum bit-error rate is observed in the crossbar structure. Bi et al. [36] carried out a total ionizing dose and single-event effects analysis on the HfO2- based 1T1R RRAM structure. The pulsed laser and Cobalt-60 are used in this work. The read

**Table 1:** Parameters used for the simulation [37].

| RRAM Model Parameters                              |  |  |  |  |  |  |  |

|----------------------------------------------------|--|--|--|--|--|--|--|

| 0-3 nm                                             |  |  |  |  |  |  |  |

| 0.5-5 nm                                           |  |  |  |  |  |  |  |

| 2 V                                                |  |  |  |  |  |  |  |

| 5 nm                                               |  |  |  |  |  |  |  |

| $20\Omega$                                         |  |  |  |  |  |  |  |

| 20 fF                                              |  |  |  |  |  |  |  |

| $200\mathrm{M}\Omega$                              |  |  |  |  |  |  |  |

| 3 nm                                               |  |  |  |  |  |  |  |

| $5 \times 10^5  \mathrm{k}\Omega$                  |  |  |  |  |  |  |  |

| 0.5 nm                                             |  |  |  |  |  |  |  |

| Effective width $(W_{eff})$ 0.5 nm DECP Parameters |  |  |  |  |  |  |  |

| 0 A                                                |  |  |  |  |  |  |  |

| 1 mA / 1 μA                                        |  |  |  |  |  |  |  |

| 20 μs                                              |  |  |  |  |  |  |  |

| 500 ns                                             |  |  |  |  |  |  |  |

| 22 μs                                              |  |  |  |  |  |  |  |

| 250 ns                                             |  |  |  |  |  |  |  |

|                                                    |  |  |  |  |  |  |  |

failures and bit errors are caused by irradiation. For space application, this analysis places greater emphasis on developing radiation-hardened RRAM. It can be observed that all the aforementioned works focus on either the crossbar or 1T1R arrays. Moreover, in our previous work, the SEU in RRAM was analyzed with respect to either the length or width of the conductive nano filament [37]. In the present work, the SEU on the RRAM device is analyzed with respect to the geometrical dimensions of the conductive nano filament, namely length and width.

#### 3. SIMULATION SETUP

The RRAM structure used for analysis is shown in Fig. 1. It consists of a top electrode, switching material, and a bottom electrode. The filament width is represented by w0. If the w0 increases, the filament will grow in the lateral direction. The length of the filament is modeled as an initial gap (x0). If the filament length is longer then x0 will be less and vice versa. If the x0 is less, the filament grows in the vertical direction [37].

Fig. 2 shows the simulation setup to study the influence of an SEU on the RRAM. The circuit setup comprises mainly the RRAM device, the resistor  $(R_H)$  which models the parasitic resistance of the switching layer, and the capacitance between the bottom and the top contacts modeled by the capacitor  $(C_P)$ . The resistor  $(R_L)$  represents the contact resistance of both the bottom and top electrodes. The double exponential current pulse (DECP) is injected at the junction of the top and switching layer to analyze the SEU. Table 1 presents the RRAM and DECP parameters incorporated in this work [37].

For the purpose of simulation, the Peking University-Stanford University RRAM spice model version 2.0-beta is being incorporated [38–41]. The single-event upset is modeled as a double exponential current pulse [42].

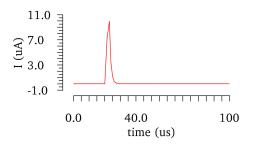

**Fig. 3:** Double exponential current pulse of  $10 \mu A$ .

Table 2: Relationship between the DECP value and its equivalent charge [37].

|   | DECP   | Equivalent Charge |

|---|--------|-------------------|

| • | 1 μΑ   | 1.469 pC          |

|   | 10 μΑ  | 14.69 pC          |

|   | 50 μA  | 73.5 pC           |

|   | 100 μΑ | 146.9 pC          |

|   | 250 μΑ | 367.2 pC          |

|   | 500 μA | 734.5 pC          |

|   |        |                   |

Fig. 3 shows the typical double exponential current pulse of 10  $\mu$ A. All simulations are performed using Cadence EDA. In all our simulation work, the x0 is varied from 3 to 0 nm whereas the w0 is varied from 0.5 to 5 nm. Table 2 shows the DECP values and their equivalent charge [37]. For DECP values of less than  $1 \mu A$ , the SEU has no influence on the RRAM resistance. Hence, a DECP range of 1  $\mu$ A to 500  $\mu$ A is considered for analysis purposes.

## 4. RESULTS AND DISCUSSION

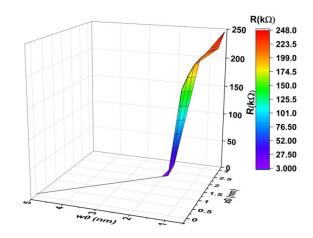

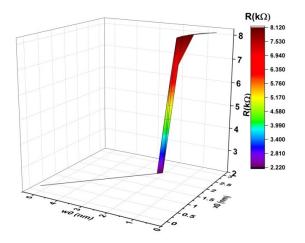

Initially, without injecting the DECP, the resistance of the RRAM is evaluated with respect to x0 and w0. Fig. 4 shows the variation in RRAM resistance versus x0and w0. As the value of x0 reduces from 3 to 0 nm, a gradual increase occurs in the filament length. The width of the filament widens as w0 increases from 0.5 to 5 nm. Therefore, the filament grows in both vertical and lateral directions. Hence, the resistance of the device shows a gradual decrement as depicted in Fig. 4. The device offers a resistance of 248 k $\Omega$  when x0 is 3 nm while w0 is 0.5 nm, representing its HRS. The resistance drops to  $3.03 \,\mathrm{k}\Omega$  when x0 is 2 nm and w0 is 2 nm, representing the LRS of the device. The device remains in LRS when  $x0 \le 2 \text{ nm}$ , while  $w0 \ge 2 \text{ nm}$ . When  $x0 \le 2 \text{ nm}$ , while  $w0 \ge 2 \text{ nm}$  both lateral and vertical growth occurs in the switching layer. This leads to an increase in current. Therefore, the resistance will drop to  $3.03 \,\mathrm{k}\Omega$ . The HRS to LRS ratio is 81.87, representing the ratio of 248.08 k $\Omega$ to  $3.03 \text{ k}\Omega$ .

The current flowing through the RRAM cell ( $I_{cell}$ ) is given by

$$I_{cell} = I_{sub-oxide} + I_{CF} + I_{Pristine} \tag{1}$$

where  $I_{CF}$  denotes the conduction caused by the nano

3D graph of resistance of the RRAM without injecting the DECP.

filament, I<sub>Pristine</sub> represents the conduction due to unswitched pristine oxide, and  $I_{sub-oxide}$  the conduction through switchable sub-oxide [42]. Since the growth of the nano conductive filament takes place both vertically and laterally, the  $I_{CF}$  term contributes significantly. Hence, the overall Icell increases and the RRAM performance decreases.

The various currents in Eq. (1) can be elaborated as shown in Eqs. (2), (3), and (4), respectively.

$$I_{CF} = F\pi\sigma_{CF}r_{CF}^2 \tag{2}$$

$$I_{sub-oxide} = F\pi\sigma_{OX} \left( r_{CF\,\text{max}}^2 - r_{CF}^2 \right) \tag{3}$$

$$I_{Pristine} = S_{cell} A F^2 \exp\left(\frac{-B}{F}\right) \tag{4}$$

where  $=\frac{m_e q^3}{8\pi h m_e^{OX} \phi_b};$ electric field =  $\left(\frac{V_{cell}}{I_{cell}}\right)$ ;  $\frac{8\pi\sqrt{2m_e^{OX}}}{3hq}$ h Planck constant; section of the device;  $S_{cell}$ metal-oxide barrier height;  $\phi_b$ radius of the conductive filament;  $r_{CF}$  $r_{CF \max}$  radius of the switchable oxide; electrical conductivity;

$m_e \ m_e^{OX}$ effective electron masses into the cathode;

effective electron masses into the oxide [43].

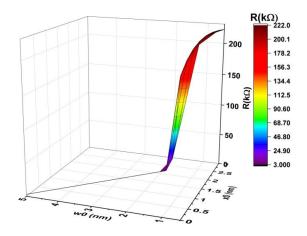

Firstly, to analyze the impact of an SEU on the RRAM, a DECP of 1  $\mu$ A is injected. The initial gap length (x0) and the width of the filament (w0) are varied simultaneously. The current flowing through the RRAM is measured. The resistance of the device is evaluated by the ratio of the applied input voltage  $(V_{in})$  to the current flowing. The graph of RRAM resistance is plotted with respect to x0 and w0 as shown in Fig. 5 when a DECP of  $1 \mu A$ is injected. The injected current pulse causes more

**Fig. 5:** 3D graph of an SEU on RRAM when the DECP =  $1 \mu A$ .

**Fig. 6:** 3D graph of an SEU on RRAM when the DECP =  $10 \mu A$ .

redox reactions inside the switching material of the device. Hence, an outgrowth of the filament will occur in both lateral and vertical directions. Therefore, there will be a drop in resistance compared to the state of RRAM without injecting the DECP. In this case,  $222\,\mathrm{k}\Omega$  corresponds to  $x0=3\,\mathrm{nm}$  and  $w0=0.5\,\mathrm{nm}$ . This can be considered as the HRS, while the LRS of  $3.03\,\mathrm{k}\Omega$  corresponds to  $x0\leq 2\,\mathrm{nm}$  and  $w0\geq 2\,\mathrm{nm}$ . The HRS to LRS ratio is 73.26 which is the ratio of  $222\,\mathrm{k}\Omega$  to  $3.03\,\mathrm{k}\Omega$ .

The physical mechanism of the SEU on the RRAM can be explained as follows: excess holes and oxygen vacancies are generated due to irradiation. The space charge area within the switching layer is altered due to these excess charge carriers. These carriers tend to accumulate at the interface of the switching layer as well as near the top contact. This leads to the Shottky barrier bending and the height being lowered. The Shottky barrier height  $(\Phi)$  and the current density (J) due to irradiation is given by

Fig. 7: 3D graph of an SEU on RRAM when the DECP =  $50 \mu A$ .

$$J = A^* T^2 \exp\left(\frac{q\sqrt{qE/4\pi\varepsilon_i} - q\Phi}{kT}\right)$$

(5)

where  $A^*$  is the Richardson constant, q is the electron charge,  $\varepsilon_i$  is the insulator permittivity, k is the Boltzmann constant, T is the absolute temperature, and E is the applied electric field [44–45].

The development of the conductive nano filament in both the lateral and vertical direction is contributed by the newly generated oxygen vacancies due to irradiation. As well as the aforementioned process, there is also an increase in the number of conductive nano filaments. Therefore, a reduction in the RRAM resistance can be observed [44].

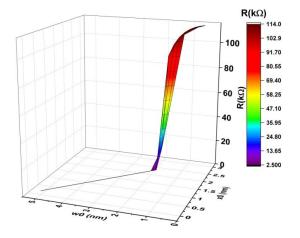

Secondly, a DECP of  $10\,\mu\text{A}$  is injected. Compared to the previous case (DECP =  $1\,\mu\text{A}$ ), the injected DECP further enhances the rate of redox reactions. This leads to the development of the length and width in the conductive filament. The graph of RRAM resistance versus x0 and w0 is presented in Fig. 6. The variation of the resistance is in terms of kiloohms for  $x0 > 2\,\text{nm}$  and  $w0 < 2\,\text{nm}$ . It can be observed that the resistance offered is  $113.6\,\text{k}\Omega$  when  $x0 = 3\,\text{nm}$  and  $w0 = 0.5\,\text{nm}$ . As the filament grows, the resistance drops to  $2.99\,\text{k}\Omega$  for  $x0 \le 2\,\text{nm}$ , while  $w0 \ge 2\,\text{nm}$ . The HRS to LRS ratio is 37.99 for which the ratio is  $113.6\,\text{k}\Omega$  to  $2.99\,\text{k}\Omega$ .

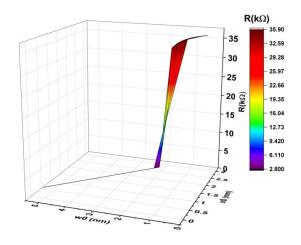

Thirdly, a DECP of 50  $\mu$ A is injected, which is equivalent to depositing a charge of 73.5 pC. Fig. 7 shows the plot of RRAM resistance versus x0 and w0 when a DECP of 50  $\mu$ A is injected. Compared to the DECP of 10  $\mu$ A, the rate of redox reactions is enhanced by almost five times. Hence, for x0=3 nm and w0=0.5 nm itself, the device demonstrates a resistance of 35.88 k $\Omega$ . This shows the impact of a DECP in the formation of a conductive filament to some extent. The resistance variation is only a few hundred ohms for x0>2 nm and w0<2 nm. This contributes to a decrease in the resistance of the device. Finally, the device offers a resistance of 2.83 k $\Omega$  for  $x0\leq 2$  nm, while  $w0\geq 2$  nm. The HRS to LRS ratio is

Fig. 8: 3D graph of an SEU on RRAM when the DECP =  $100 \mu A$ .

**Fig. 9:** 3D graph of an SEU on RRAM when the DECP =  $250 \mu A$ .

12.67 which is the ratio of 35.88 k $\Omega$  to 2.83 k $\Omega$ .

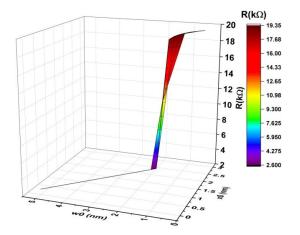

Furthermore, a DECP of  $100~\mu\mathrm{A}$  is injected to observe the influence of an SEU on RRAM resistance. The  $100~\mu\mathrm{A}$  corresponds to an equivalent charge of  $146.9~\mathrm{pC}$ . Fig. 8 shows the plot of RRAM resistance versus x0 and w0. It can be observed that the filament has grown by 90% both in lateral and vertical directions. Hence, there is a greater reduction in resistance. Therefore,  $19.34~\mathrm{k}\Omega$  of resistance is observed when  $x0=3~\mathrm{nm}$  and  $w0=0.5~\mathrm{nm}$ . As the x0 decreases and w0 increments, the resistance drops in terms of a few hundred ohms. Finally, the least resistance state of  $2.65~\mathrm{k}\Omega$  is observed for  $x0\leq 2~\mathrm{nm}$  while  $w0\geq 2~\mathrm{nm}$ . The ratio of HRS to LRS is  $7.3~\mathrm{which}$  is the ratio of  $19.34~\mathrm{k}\Omega$  to  $2.65~\mathrm{k}\Omega$ .

In this case, a DECP of 250  $\mu$ A is injected. Fig. 9 shows the variation of RRAM resistance versus x0 and w0 with a DECP of 250  $\mu$ A. The 250  $\mu$ A corresponds to a charge of 367.2 pC. From the simulations, it can be observed that the resistance variation is limited to a few tens of ohms compared to the previous cases. The resistance observed is  $8.114 \,\mathrm{k}\Omega$  for  $x0 = 3 \,\mathrm{nm}$  and  $w0 = 0.5 \,\mathrm{nm}$ . The device remains in a resistance of  $2.23 \,\mathrm{k}\Omega$  for  $x0 \leq 2 \,\mathrm{nm}$ , while

**Fig. 10:** 3D graph of an SEU on RRAM when the DECP =  $500 \mu A$ .

**Table 3:** Comparison of resistance of RRAM with respect to the dimensions of a conductive nano filament under different DECPs.

|      |      | RRAM Resistance (kΩ) |      |       |       |        |        |        |  |  |

|------|------|----------------------|------|-------|-------|--------|--------|--------|--|--|

| x0   | w0   | Without              | DECP | DECP  | DECP  | DECP   | DECP   | DECP   |  |  |

| (nm) | (nm) | DECP                 | 1 μΑ | 10 μA | 50 μA | 100 μΑ | 250 μΑ | 500 μA |  |  |

| 3    | 0.5  | 248.08               | 222  | 113.6 | 35.88 | 19.34  | 8.114  | 4.130  |  |  |

| 2.5  | 1.25 | 215.76               | 195  | 106   | 35.11 | 19.11  | 8.07   | 4.115  |  |  |

| 2    | 2    | 3.03                 | 3.03 | 2.99  | 2.83  | 2.65   | 2.23   | 1.76   |  |  |

| 1.5  | 2.75 | 3.03                 | 3.03 | 2.99  | 2.83  | 2.65   | 2.23   | 1.76   |  |  |

| 1    | 3.5  | 3.03                 | 3.03 | 2.99  | 2.83  | 2.65   | 2.23   | 1.76   |  |  |

| 0.5  | 4.25 | 3.03                 | 3.03 | 2.99  | 2.83  | 2.65   | 2.23   | 1.76   |  |  |

| 0    | 5    | 3.03                 | 3.03 | 2.99  | 2.83  | 2.65   | 2.23   | 1.76   |  |  |

$w0 \ge 2$  nm. The ratio of HRS to LRS will be 3.64 which is the ratio of  $8.114 \text{ k}\Omega$  to  $2.23 \text{ k}\Omega$ .

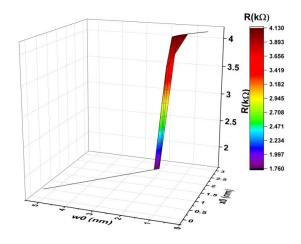

Lastly, a DECP of  $500\,\mu\mathrm{A}$  is injected. The  $500\,\mu\mathrm{A}$  corresponds to an equivalent charge of  $734.5\,\mathrm{pC}$ . Fig. 10 shows the variation in RRAM resistance versus x0 and w0 when  $500\,\mu\mathrm{A}$  is injected. From the simulations, it can be observed that the filament has grown by 98%. Hence, the resistance is  $4.130\,\mathrm{k}\Omega$  when  $x0=3\,\mathrm{nm}$  and  $w0=0.5\,\mathrm{nm}$ , whereas the device offers resistance of  $1.76\,\mathrm{k}\Omega$  for  $x0\leq 2\,\mathrm{nm}$ , while  $w0\geq 2\,\mathrm{nm}$ . Therefore, the ratio of HRS to LRS still further reduces to 2.34. The resistance variations are limited to a few ohms for every decrement in x0 and increment in w0. Table 3 presents an overall comparison of the entire work.

# 5. CONCLUSION

In this work, the impact of an SEU on RRAM is analyzed with respect to the dimensions of the conductive filament. The impact represents the resistance of the device changes from HRS to LRS. As well as the resistance, the HRS to LRS ratio has also been reduced from 81.87 to 2.34. The memory window size will be the lowest. Suitable hardening techniques are proposed to mitigate the SEU effects on the RRAM. Further analysis

can be carried out on multi-nano conductive filaments. Apart from the length and width variations, the thickness variation of the filament can also be considered in future work.

## **REFERENCES**

- [1] N. Cao, S. B. Nasir, S. Sen, and A. Raychowdhury, "Self-optimizing IoT wireless video sensor node with in-situ data analytics and context-driven energy-aware real-time adaptation," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 9, pp. 2470–2480, Sep. 2017.

- [2] J. S. Meena, S. M. Sze, U. Chand, and T.-Y. Tseng, "Overview of emerging nonvolatile memory technologies," *Nanoscale Research Letters*, vol. 9, no. 1, 2014, Art. no. 526.

- [3] S. Yu and P.-Y. Chen, "Emerging memory technologies: Recent trends and prospects," *IEEE Solid-State Circuits Magazine*, vol. 8, no. 2, pp. 43–56, 2016.

- [4] F. García-Redondo and M. López-Vallejo, "On the design and analysis of reliable RRAM-CMOS hybrid circuits," *IEEE Transactions on Nanotechnology*, vol. 16, no. 3, pp. 514–522, May 2017.

- [5] D. Ielmini, "Modeling the universal set/reset characteristics of bipolar RRAM by field- and temperature-driven filament growth," *IEEE Transactions on Electron Devices*, vol. 58, no. 12, pp. 4309–4317, Dec. 2011.

- [6] J. R. Jameson et al., "Quantized conductance in Ag/GeS<sub>2</sub>/W conductive-bridge memory cells," *IEEE Electron Device Letters*, vol. 33, no. 2, pp. 257–259, Feb. 2012.

- [7] S. Tappertzhofen, I. Valov, and R. Waser, "Quantum conductance and switching kinetics of AgI-based microcrossbar cells," *Nanotechnology*, vol. 23, no. 14, Mar. 2012, Art. no. 145703.

- [8] T. Tsuruoka, T. Hasegawa, K. Terabe, and M. Aono, "Conductance quantization and synaptic behavior in a Ta<sub>2</sub>O<sub>5</sub>-based atomic switch," *Nanotechnology*, vol. 23, no. 43, 2012, Art. no. 435705.

- [9] X. Zhu *et al.*, "Observation of conductance quantization in oxide-based resistive switching memory," *Advanced Materials*, vol. 24, no. 29, pp. 3941–3946, Jun. 2012.

- [10] S. Long *et al.*, "Quantum-size effects in hafnium-oxide resistive switching," *Applied Physics Letters*, vol. 102, no. 18, 2013, Art. no. 183505.

- [11] E. Miranda, S. Kano, C. Dou, K. Kakushima, J. Suñé, and H. Iwai, "Nonlinear conductance quantization effects in CeO<sub>x</sub>/SiO<sub>2</sub>-based resistive switching devices," *Applied Physics Letters*, vol. 101, no. 1, 2012, Art. no. 012910.

- [12] C. Hu, M. D. McDaniel, J. G. Ekerdt, and E. T. Yu, "High ON/OFF ratio and quantized conductance in resistive switching of TiO<sub>2</sub> on silicon," *IEEE Electron Device Letters*, vol. 34, no. 11, pp. 1385–1387, Nov. 2013.

- [13] S. Gao et al., "Resistive switching and conductance

- quantization in  $Ag/SiO_2/indium$  tin oxide resistive memories," *Applied Physics Letters*, vol. 105, no. 6, 2014, Art. no. 063504.

- [14] R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories - nanoionic mechanisms, prospects, and challenges," *Advanced Materials*, vol. 21, no. 25–26, pp. 2632–2663, Jul. 2009.

- [15] F. Pan, S. Gao, C. Chen, C. Song, and F. Zeng, "Recent progress in resistive random access memories: Materials, switching mechanisms, and performance," *Materials Science and Engineering: R: Reports*, vol. 83, pp. 1–59, Sep. 2014.

- [16] W. Banerjee, S. Z. Rahaman, A. Prakash, and S. Maikap, "High- $\kappa$  Al<sub>2</sub>O<sub>3</sub>/WO<sub>x</sub> bilayer dielectrics for low-power resistive switching memory applications," *Japanese Journal of Applied Physics*, vol. 50, no. 10S, 2011, Art. no. 10PH01.

- [17] Y. L. Song, Y. Liu, Y. L. Wang, M. Wang, X. P. Tian, L. M. Yang, and Y. Y. Lin, "Low reset current in stacked  ${\rm AlO_x/WO_x}$  resistive switching memory," *IEEE Electron Device Letters*, vol. 32, no. 10, pp. 1439–1441, Oct. 2011.

- [18] Y.-C. Huang, W.-L. Tsai, C.-H. Chou, C.-Y. Wan, C. Hsiao, and H.-C. Cheng, "High-performance programmable metallization cell memory with the pyramid-structured electrode," *IEEE Electron Device Letters*, vol. 34, no. 10, pp. 1244–1246, Oct. 2013.

- [19] H.-D. Kim, M. J. Yun, S. M. Hong, and T. G. Kim, "Effect of nanopyramid bottom electrodes on bipolar resistive switching phenomena in nickel nitride films-based crossbar arrays," *Nanotechnology*, vol. 25, no. 12, 2014, Art. no. 125201.

- [20] Y.-J. Huang, S.-C. Chao, D.-H. Lien, C.-Y. Wen, J.-H. He, and S.-C. Lee, "Dual-functional memory and threshold resistive switching based on the push-pull mechanism of oxygen ions," *Scientific Reports*, vol. 6, 2016, Art. no. 23945.

- [21] Q. Liu et al., "Controllable growth of nanoscale conductive filaments in solid-electrolyte-based ReRAM by using a metal nanocrystal covered bottom electrode," ACS Nano, vol. 4, no. 10, pp. 6162–6168, Sep. 2010.

- [22] Y.-T. Tsai *et al.*, "Influence of nanocrystals on resistive switching characteristic in binary metal oxides memory devices," *Electrochemical and Solid-State Letters*, vol. 14, no. 3, 2011, Art. no. H135.

- [23] J. Yoon *et al.*, "Excellent switching uniformity of Cu-doped  $MoO_x/GdO_x$  bilayer for nonvolatile memory applications," *IEEE Electron Device Letters*, vol. 30, no. 5, pp. 457–459, May 2009.

- [24] K.-C. Chang *et al.*, "The effect of silicon oxide based RRAM with tin doping," *Electrochemical and Solid-State Letters*, vol. 15, no. 3, 2012, Art. no. H65.

- [25] U. Celano *et al.*, "Three-dimensional observation of the conductive filament in nanoscaled resistive memory devices," *Nano Letters*, vol. 14, no. 5, pp. 2401–2406, Apr. 2014.

- [26] X. Wu *et al.*, "Evolution of filament formation in Ni/HfO<sub>2</sub>/SiO<sub>x</sub>/Si-based RRAM devices," *Advanced Electronic Materials*, vol. 1, no. 11, Nov. 2015, Art. no. 1500130.

- [27] T. S. Lee, N. J. Lee, H. Abbas, H. H. Lee, T.-S. Yoon, and C. J. Kang, "Compliance current-controlled conducting filament formation in tantalum oxide-based RRAM devices with different top electrodes," ACS Applied Electronic Materials, vol. 2, no. 4, pp. 1154–1161, Apr. 2020.

- [28] A. Oates, "7 reliability of silicon integrated circuits," in *Reliability Characterisation of Electrical and Electronic Systems*, J. Swingler, Ed. Oxford, UK: Woodhead Publishing, 2015, pp. 115–141.

- [29] Y.-P. Fang and A. S. Oates, "Thermal neutroninduced soft errors in advanced memory and logic devices," *IEEE Transactions on Device and Materials Reliability*, vol. 14, no. 1, pp. 583–586, Mar. 2014.

- [30] D. Chen, E. Wilcox, R. L. Ladbury, C. Seidleck, H. Kim, A. Phan, and K. A. LaBel, "Heavy ion and proton-induced single event upset characteristics of a 3-D NAND flash memory," *IEEE Transactions on Nuclear Science*, vol. 65, no. 1, pp. 19–26, Jan. 2018.

- [31] V. Zajic and P. Thieberger, "Heavy ion linear energy transfer measurements during single event upset testing of electronic devices," *IEEE Transactions on Nuclear Science*, vol. 46, no. 1, pp. 59–69, Feb. 1999.

- [32] A. K. Sharma, Semiconductor memories: technology, testing, and reliability. Piscataway, NJ, USA: Wiley-IEEE Press, 1997.

- [33] R. Liu, D. Mahalanabis, H. J. Barnaby, and S. Yu, "Investigation of single-bit and multiple-bit upsets in oxide RRAM-based 1T1R and crossbar memory arrays," *IEEE Transactions on Nuclear Science*, vol. 62, no. 5, pp. 2294–2301, Oct. 2015.

- [34] W. G. Bennett *et al.*, "Dynamic modeling of radiation-induced state changes in HfO<sub>2</sub>/Hf 1T1R RRAM," *IEEE Transactions on Nuclear Science*, vol. 61, no. 6, pp. 3497–3503, Dec. 2014.

- [35] R. Liu, H. J. Barnaby, and S. Yu, "System-level analysis of single event upset susceptibility in RRAM architectures," Semiconductor Science and Technology, vol. 31, no. 12, 2016, Art. no. 124005.

- [36] J. Bi, Y. Duan, K. Xi, and B. Li, "Total ionizing dose and single event effects of 1Mb HfO<sub>2</sub>-based resistive-random-access memory," *Microelectronics Reliability*, vol. 88–90, pp. 891–897, Sep. 2018.

- [37] H. M. Vijay and V. N. Ramakrishnan, "Conductive filament variation of RRAM and its impact on single event upset," *Transactions on Electrical and Electronic Materials*, 2021.

- [38] H. Li, P. Huang, B. Gao, B. Chen, X. Liu, and J. Kang, "A SPICE model of resistive random access memory for large-scale memory array simulation," *IEEE Electron Device Letters*, vol. 35, no. 2, pp. 211–213, Feb. 2014.

- [39] X. Guan, S. Yu, and H.-S. P. Wong, "A SPICE compact model of metal oxide resistive switching memory with variations," *IEEE Electron Device Letters*, vol. 33, no. 10, pp. 1405–1407, Oct. 2012.

- [40] H.-S. P. Wong et al., "Metal-oxide RRAM," Proceedings of the IEEE, vol. 100, no. 6, pp. 1951–1970, Jun. 2012

- [41] H. Li et al., "Variation-aware, reliability-emphasized design and optimization of RRAM using SPICE model," in 2015 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2015, pp. 1425–1430.

- [42] F. Wang and V. D. Agrawal, "Single event upset: An embedded tutorial," in 21st International Conference on VLSI Design (VLSID 2008), 2008, pp. 429–434.

- [43] M. Bocquet, D. Deleruyelle, H. Aziza, C. Muller, J.-M. Portal, T. Cabout, and E. Jalaguier, "Robust compact model for bipolar oxide-based resistive switching memories," *IEEE Transactions on Electron Devices*, vol. 61, no. 3, pp. 674–681, Mar. 2014.

- [44] F. Yuan, S. Shen, and Z. Zhang, "γ-ray irradiation effects on TiN/HfOx/Pt resistive random access memory devices," in 2015 IEEE Aerospace Conference, 2015.

- [45] J. S. Bi *et al.*, "The impact of X-ray and proton irradiation on HfO<sub>2</sub>/Hf-based bipolar resistive memories," *IEEE Transactions on Nuclear Science*, vol. 60, no. 6, pp. 4540–4546, Dec. 2013.

Vijay H. M. received the M.Tech. and B.E. degree in electronics engineering from Visvesvaraya Technological University (VTU), Belgaum, India in 2011, and Kuvempu University, Shimoga, India in 2005, respectively. He is currently pursuing Ph.D. in the Department of Micro and Nanoelectronics, School of Electronics Engineering, Vellore Institute of Technology (VIT), Vellore, India since 2016. His present research interest includes ReRAMs and memristor based memories. He published

many research articles in reputed journals and presented papers in conferences.

V. N. Ramakrishnan received the M.E. and Ph.D. degree in electronics engineering from Anna University, India, in 2004 and 2015 respectively. He is currently working as an Associate Professor in the Department of Micro and Nanoelectronics, School of Electronics Engineering, Vellore Institute of Technology (VIT), Vellore, India. His present research interest includes nano-scale device modeling, Design of GaN based vertical power MOSFETs and ReRAMs. He published many research

articles in reputed journals and presented papers in conferences.