# A Phase Lead-Lag Synchronous Reference Frame Phase-locked loop for Grid Synchronization of a Single-Phase Inverter

Chuttchaval Jeraputra<sup>†</sup>, Jetnarong Pongpaiboon, Thamvarit Singhavilai, and Supun Tiptipakorn, Non-members

#### ABSTRACT

In this study, a phase lead-lag synchronous reference frame phase-locked loop (SRF-PLL) is proposed for the grid connection of a single-phase inverter. A tuned filter is employed to enable the phase of the input voltage to be advanced or delayed by ±45 degrees with respect to the grid voltage. The generated orthogonal signals are fed into Park's transformation. Only the quadrature-phase signal is regulated to zero using a PI controller. Its output determines the estimated frequency. The phase angle is obtained by integrating the estimated frequency. The linearized model of the proposed SRF-PLL is developed and stability analysis is discussed. The viability of the proposed method is tested under computer simulation using MATLAB/Simulink. The method is then implemented on a 32-bit microcontroller and tested with a programmable AC source. The results positively confirm the effectiveness of the method.

**Keywords**: Phase Lead-Lag, Synchronization, Single-Phase Inverter, Phase-Locked Loop

## 1. INTRODUCTION

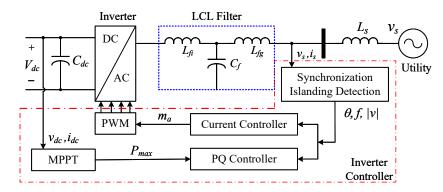

At present, electrical power systems are migrating from radial power systems toward the distributed generation (DG) paradigm. This provides an opportunity for alternative energy sources, such as wind turbines, water turbines, and solar cells to be integrated into the grid. The integration of DGs into the utility grid requires power inverters to control the real power and reactive power fed into the grid, as well as regulating harmonic currents compliant with the requirements. Fig. 1 shows a typical control structure for a single-phase grid-tied inverter. One of the most important parts in the control of a power inverter is the synchronization unit which monitors magnitude, frequency, and phase of the grid voltage. When the penetration level of the

grid-tied power inverter is high, accurate and robust phase detection is essential.

Several methods for phase and frequency detection of a single-phase voltage have been proposed in previous works. Sakamoto *et al.* proposed quadrature two-phase estimation by delaying the single-phase grid voltage by one quarter of a period [1]. An SRF-PLL is applied to estimate the frequency and phase of the grid. If the frequency of the grid voltage varies, a nonzero average phase error and double frequency oscillatory error will occur, significantly degrading the performance of the method.

Golestan *et al.* presented a small signal model and discussed the performance enhancement of transfer delay based PLLs [2]. The phase error can be corrected by adding a linear phase compensator [3]. The use of two cascaded  $\alpha\beta$ -DSC operators can effectively reject the double frequency oscillatory error. Additional cascaded  $\alpha\beta$ -DSC operators with appropriate delay factors can improve filtering capability in the presence of harmonic voltages [4, 5]. The method performance under DC offset was not evaluated.

Amuda et al. proposed inverse Park's transformation to generate orthogonal two-phase voltage [6], employing low pass filters to improve filtering capability. However, these filters have an adverse effect on dynamic response. Hadjidemetriou et al. proposed an improvement by using inverse Park's transformation for each harmonic component [7]. It results in better immunity to distorted harmonic voltage, but had the drawbacks of detection inaccuracy and computational burden. Ciobotaru et al. proposed the second-order generalized integrator (SOGI) to create orthogonal two-phase voltage [8]. The method is frequency-adaptive and capable of detecting the phase under frequency variation. The DC offset cancellation process was implemented using a low pass filter [9], although the harmonic filtering capability is compromised at high frequency. Alternatively, the DC component can be estimated and rejected by an integrator loop [10]. High order harmonic filtering capability and DC offset rejection can be improved by cascading two SOGIs [11]. Rodriguez et al. proposed SOGIs operating in parallel, with each unit tuned specifically for each harmonic order [12]. A fast response can be achieved, but it is sensitive to inter-harmonics or subharmonics in the grid voltage.

Fang et al. proposed amplitude and phase estimation

Manuscript received on August 18, 2021; revised on October 6, 2021; accepted on October 31, 2021. This paper was recommended by Associate Editor Yuttana Kumsuwan.

The authors are with the Department of Electrical Engineering, Mahidol University, Nakhon Pathom, Thailand.

<sup>&</sup>lt;sup>†</sup>Corresponding author: chuttchaval.jer@mahidol.ac.th

<sup>©2022</sup> Author(s). This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 4.0 License. To view a copy of this license visit: https://creativecommons.org/licenses/by-nc-nd/4.0/.

Digital Object Identifier: 10.37936/ecti-eec.2022201.246117

Fig. 1: Control structure of a single-phase grid-connected inverter.

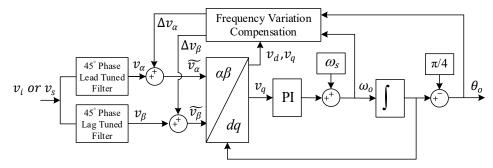

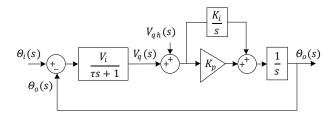

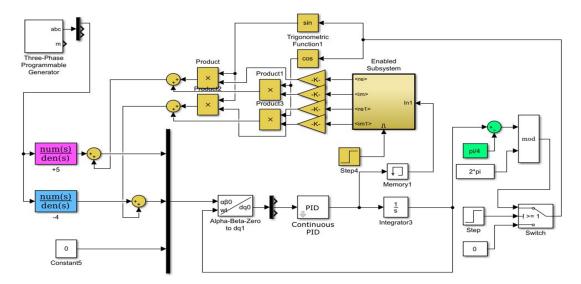

Fig. 2: Proposed phase lead-lag SRF-PLL.

for single-phase PLL [13]. The component orthogonal to the grid voltage is generated by utilizing the estimated amplitude and phase derived from the PLL output. In the case of a distorted harmonic voltage, amplitude and phase estimation can be implemented for each harmonic order. The method has a reasonable computational burden, while the DC offset rejection was not evaluated. Karimi-Ghartemani and Iravani proposed an enhanced single-phase PLL [14] to track the phase of the grid voltage even if phase jump occurs. In steady state, it can track the phase of the grid voltage with zero errors. In addition, the DC offset can be estimated by an integrator [10]. The detection of harmonic voltages was proposed in [15] to eliminate each harmonic component, but the computation is intensive.

As discussed, none of the solutions proposed comprehensive methods to ensure correct phase detection for practical utility grids. This paper proposes a phase lead-lag SRF-PLL. Orthogonal two-phase voltages are realized by a 45° phase-lead tuned filter and a 45° phase-lag tuned filter. In addition, frequency variation compensation is introduced to correct the estimated phase if the grid voltage frequency varies. The proposed algorithm is simple and the computation reasonable. It is robust against distorted harmonic voltage, DC offset, phase jump, and frequency variation.

This paper is organized as follows. The phase lead-lag SRF-PLL is proposed in Section 2 while the linearized model and controller design is discussed in Section 3. The feasibility of the proposed method is validated by simulation using MATLAB/Simulink in Section 4. The algorithm is implemented on a 32-bit microcontroller

STM32F429ZIT6 and evaluated under six voltage conditions, while the results are discussed in Section 5. The conclusion is provided in Section 6.

## 2. PROPOSED PHASE LEAD-LAG SRF-PLL

The phase lead-lag SRF-PLL is proposed in Fig. 2. The single-phase grid voltage is filtered by a +45° phase-lead tuned filter and a -45° phase-lag tuned filter. Their output signals are compensated when the frequency of the grid differs from the power or nominal frequency of 50 Hz. They are fed into Park's transformation which receives the phase angle from the integrator. quadrature-phase voltage  $v_q$  provides the phase error. It is then regulated to zero by a PI controller the output signal of which determines the frequency of the input voltage. The phase angle of the input voltage is obtained by integrating the frequency. However, the acquired phase advances the phase of the grid by +45°. It is necessary for the 45° phase to be subtracted from the integrator's output to yield the actual phase angle of the input voltage.

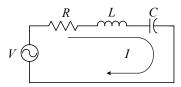

The basic idea of implementing  $+45^{\circ}$  and  $-45^{\circ}$  tuned filters is derived from a series *RLC* circuit as shown in Fig. 3. The relationship between the input voltage and the current through the *RLC* series circuit can be expressed by a transfer function in the frequency domain as

$$T(s) = k_L \frac{s}{s^2 + \frac{\omega_n}{O}s + \omega_n^2}$$

(1)

which for a series RLC circuit in Fig. 3,

Fig. 3: Series RLC circuit.

$$k_L = \frac{1}{L}, \quad \omega_n = \frac{1}{\sqrt{LC}}, \quad \xi = \frac{1}{2Q}, \quad Q = \frac{1}{R}\sqrt{\frac{L}{C}},$$

where  $\omega_n$  is the natural frequency,  $\xi$  is the damping ratio, and *Q* is the load quality factors.

### 2.1 45° Phase-Lead Tuned Filter

To design the phase-lead tuned filter, the relationship between the resonant frequency  $\omega_n$  and the load quality factor Q must firstly be derived to achieve the unity gain and +45° phase-lead at the nominal frequency of 50 Hz. These are expressed as

$$\angle T(s)|_{s=j\omega_s} = \frac{\pi}{4}$$

(2)

$$|T(s)|_{s=i\omega} = 1 \tag{3}$$

where the nominal frequency is denoted by  $\omega_s$  (rad/s). The natural frequency  $\omega_n$  yielding the +45° phase lead at 50 Hz and the constant gain  $k_L$  yielding the unity gain can be expressed as

$$\omega_{n\alpha} = \frac{\frac{\omega_s}{Q_\alpha} + \sqrt{\left(\frac{\omega_s}{Q_\alpha}\right)^2 + \left(2\omega_s\right)^2}}{2} \tag{4}$$

$$k_{L\alpha} = \sqrt{\left(\frac{\omega_{n\alpha}^2 - \omega_s^2}{\omega_s}\right)^2 + \left(\frac{\omega_{n\alpha}}{Q_\alpha}\right)^2}.$$

(5)

It should be noted that the lower the chosen Q factor, the faster the tuned filter responds. However, if it is too small, the harmonic filtering capability of the tuned filter will be compromised. The tuned filter can achieve 45° phase displacement, harmonic filtering capability, and DC rejection.

### 2.2 45° Phase-Lag Tuned Filter

Designing the phase-lag tuned filter can be done in a similar way to the design of the phase-lead tuned filter. The achievement of the unity gain and -45° phase-lag at the power frequency 50 Hz can be satisfied by the following equations:

$$\angle T(s)|_{s=j\omega_s} = -\frac{\pi}{4} \tag{6}$$

$$|T(s)|_{s=j\omega_s}=1. (7)$$

**Table 1:** Designed parameters.

| Parameters | Phase-Lead<br>Tuned Filter | Phase-Lag<br>Tuned Filter |

|------------|----------------------------|---------------------------|

| Q          | 5                          | 4                         |

| $k_L$      | 98                         | 98                        |

| $\omega_n$ | 347.14                     | 277.33                    |

The natural frequency and the constant gain  $k_L$  are solved and expressed as

$$\omega_{n\beta} = \frac{-\frac{\omega_s}{Q_{\beta}} + \sqrt{\left(\frac{\omega_s}{Q_{\beta}}\right)^2 + (2\omega_s)^2}}{2}$$

$$k_{L\beta} = \sqrt{\left(\frac{\omega_{n\beta}^2 - \omega_s^2}{\omega_s}\right)^2 + \left(\frac{\omega_{n\beta}}{Q_{\beta}}\right)^2}.$$

(8)

$$k_{L\beta} = \sqrt{\left(\frac{\omega_{n\beta}^2 - \omega_s^2}{\omega_s}\right)^2 + \left(\frac{\omega_{n\beta}}{Q_\beta}\right)^2}.$$

(9)

It is observed that the natural frequency of the phase lag tuned filter is slightly less than that of the phase lead one. The design of both filters is provided as examples in the following section.

### 2.3 Design Example

The phase lead and lag tuned filters are designed to satisfy phase displacement and unity gain constraints Eqs. (2), (3), (6), and (7). It is suggested that if harmonic filtering capability is of primary concern, the Q factor should be large and in a range of 4-5. This selection would result in the natural frequency being near to the nominal frequency and harmonics can be suppressed effectively, although it slows down transient response of the phase detection under sudden phase or frequency jump. If dynamic response becomes the first priority, the Q factor should be small and in a range of 0.05–0.1, though pre-filtering of harmonics may be required if the input voltage is highly distorted.

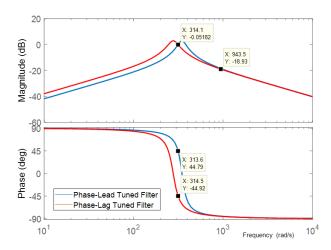

As suggested, the designed parameters are presented in Table 1. The natural frequency of the phase-lead tuned filters is slightly greater than the nominal frequency and vice versa for the phase-lag tuned filter. Fig. 4 shows frequency responses of the designed tuned filters. The unity gain and phase displacement of  $\pm 45^{\circ}$  at the nominal frequency can be achieved. It is observed that both filters are able to evenly attenuate high-order harmonics and remove DC offset from the input voltage. The attenuation gain at the third harmonic is sufficient to effectively suppress harmonic voltage of the practical grid. For higher order harmonics, their gains proportionally decrease at a rate of  $-20 \, dB$  per decade. As a result, the proposed method is robust to harmonic voltage distortion as well as DC offset.

Fig. 4: Frequency response of phase-lead and phase-lag tuned filters.

## 3. LINEARIZED MODEL AND STABILITY ANALYSIS

A linearized model is derived involving Park's transformation in conjunction with phase-lead and phase-lag tuned filters. It should be noted that the effect of frequency variation compensation is not taken into consideration at the present time. For simplicity, it is assumed that the input voltage is purely sinusoidal with the nominal magnitude and frequency, defined by

$$v_i(t) = V_i \cos(\omega_i t + \phi_i) \tag{10}$$

where the voltage amplitude, frequency, and phase are denoted by  $V_i$ ,  $\omega_i$  and  $\phi_i$ , respectively. After applying input voltage to both tuned filters, the orthogonal two-phase voltage  $v_{\alpha}$  and  $v_{\beta}$  in Fig. 2 can be expressed as follows:

$$v_{\alpha}(t) = V_{i} \cos\left(\omega_{i}t + \phi_{i} + \frac{\pi}{4}\right) + A_{\alpha} \cos\left(\omega_{n\alpha}\sqrt{1 - \left(\frac{1}{2Q_{\alpha}}\right)^{2}t + \alpha}\right) e^{-\frac{\omega_{n\alpha}}{2Q_{\alpha}}t}$$

$$(11)$$

$$v_{\beta}(t) = V_{i} \cos\left(\omega_{i}t + \phi_{i} - \frac{\pi}{4}\right) + A_{\beta} \cos\left(\omega_{n\beta}\sqrt{1 - \left(\frac{1}{2Q_{\beta}}\right)^{2}t + \beta}\right) e^{-\frac{\omega_{n\beta}}{2Q_{\beta}}t}$$

$$(12)$$

where  $A_{\alpha}$ ,  $A_{\beta}$  are the amplitudes of the oscillating terms and  $\alpha$ ,  $\beta$  denote their corresponding phase shift. These are functions of  $V_i$ ,  $\phi_i$ , and Q. The oscillating terms will exponentially decay with a time constant which can be determined from roots of the characteristic equation (Eq. (1)).

Park's transformation is employed to transform the two-phase voltages  $v_{\alpha}$  and  $v_{\beta}$  into the synchronous

reference frame [16]. The quadrature-phase voltage  $v_q$  can be expressed as

$$v_{\alpha}(t) = -v_{\alpha}(t)\sin(\theta_{0}) + v_{\beta}(t)\cos(\theta_{0})$$

(13)

$$\theta_o(t) = \int \omega_o dt + \phi_o + \frac{\pi}{4} \tag{14}$$

the estimated frequency and phase are denoted by  $\omega_o$  and  $\theta_o$ , respectively. The mathematical expression of the transformed voltage  $v_a$  is given by

$$v_q(t) = V_i \sin((\omega_i - \omega_o)t + (\phi_i - \phi_o)) - g(t) + h(t)$$

(15)

where g(t) =

$$e^{-\frac{\omega_{n\alpha}}{2Q_{\alpha}}t}\left[A_{\alpha}\cos\left(\omega_{n\alpha}\sqrt{1-\left(\frac{1}{2Q_{\alpha}}\right)^{2}t}+\alpha\right)\sin\left(\omega_{o}t+\phi_{o}+\frac{\pi}{4}\right)\right]$$

and h(t) =

$$e^{-\frac{\omega_{n\beta}}{2Q_{\beta}}t}\left[A_{\beta}\sin\left(\omega_{n\beta}\sqrt{1-\left(\frac{1}{2Q_{\beta}}\right)^{2}t+\beta}\right)\cos\left(\omega_{o}t+\phi_{o}+\frac{\pi}{4}\right)\right].$$

Under a quasi-frequency locked state, the estimated frequency is nearly equal to that of the input voltage. The oscillating terms g(t) and h(t) will exponentially decay to zero with a time constant of  $2Q/\omega_n$ , while the quadrature-phase voltage  $v_q(t)$  rises and approaches the steady state as approximated by

$$v_a(t) \approx V_i \sin(\phi_i - \phi_o)$$

. (16)

If the phase error is small, the quadrature-phase voltage can be linearized based on Taylor's series as

$$v_q(t) \approx V_i(\phi_i - \phi_o)$$

. (17)

Thus, the response due to a sudden phase jump or step phase change can be approximated by a first-order transfer function in the frequency domain as

$$\frac{V_q(s)}{\Phi_i(s) - \Phi_o(s)} = \frac{V_q(s)}{\Phi_e(s)} = \frac{V_i}{\tau s + 1}$$

$$\tau = \frac{2Q}{\omega_n}$$

(18)

where  $\tau$  denotes the time constant of a tuned filter. In the case that two tuned filters have different time constants, it is suggested that the one with a slower time constant be adopted. Fig. 5 shows a linearized model of the proposed phase lead-lag SRF-PLL. The steady state effect of the input harmonics can be modeled as a disturbance using the Laplace transform,

$$V_{qh}(s) = \mathcal{L}\left\{\Sigma_{h=3,5,7,\dots} - \nu_{\alpha h}\sin(\theta_o) + \nu_{\beta h}\cos(\theta_o)\right\}$$

(20)

Fig. 5: Linearized model of the proposed SRF-PLL.

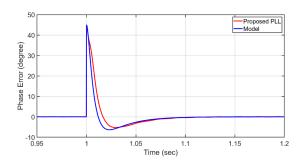

Fig. 6: Validation of the linearized model.

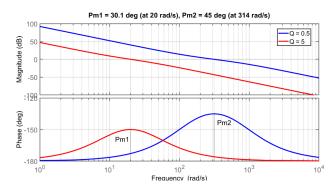

**Fig. 7:** Frequency response of the open loop transfer function  $G_{OL}(s)$ .

where  $v_{\alpha h}$  and  $v_{\beta h}$  denote the input harmonics after being attenuated by phase-lead and phase-lag tuned filters, respectively, whereas  $\mathcal{L}$  denotes the Laplace operator. Fig. 6 shows the phase error response of the linearized model and the proposed SRF-PLL when a sudden phase jump of 45° occurs. The linearized model yields nearly comparable dynamic behavior to the proposed SRF-PLL. Thus, it can be used to design controller gains and guarantee stability.

If the effect of the disturbance is ignored, the open loop transfer function with the normalized input voltage can be expressed as

$$G_{OL}(s) = \frac{\Phi_o(s)}{\Phi_e(s)}\Big|_{V_{ob}(s)=0} = K_I \frac{(\tau_z s + 1)}{s^2(\tau_p s + 1)}$$

(21)

where  $\tau_p = 2Q/\omega_n$  and  $\tau_z = K_p/K_I$ . It has double poles at the origin and one pole  $(p = -1/\tau_p)$  and one zero  $(z = -1/\tau_z)$  on the left half-plane. A zero-pole pair in Eq. (21) can provide a phase boost in the same way as a typical phase-lead controller. Based on the symmetrical optimum method [17], maximum phase boost can be achieved at the gain crossover frequency given as

Table 2: PI controller parameters.

|               | Q = 5 | Q = 0.5 |

|---------------|-------|---------|

| $K_P$         | 25    | 314     |

| $K_I$         | 360.2 | 40 882  |

| PM            | 30°   | 45°     |

| $\omega_{cf}$ | 25    | 314     |

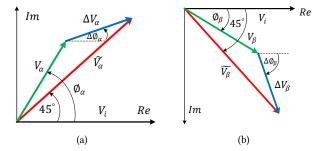

Fig. 8: Phasor of the input voltage after filtering by the tuned filters (a) phase-lead voltage and (b) phase-lag voltage.

$$\omega_{cf} = \frac{1}{\sqrt{\tau_z \tau_p}} \tag{22}$$

whereas, proper selection of the PI controller gains is obtained by

$$K_P = \omega_{cf}, \tag{23}$$

$$K_I = \tau_p K_p^3. \tag{24}$$

Fig. 7 shows the frequency response of the open loop transfer function with the load factor Q equal to 0.5 and 5. The PI controller gains are given in Table 2. It should be noted that the high load factor Q results in a low bandwidth and better harmonic filtering capability but the slow response is a trade-off.

A good compromise could be achieved when the load factor Q is about 0.5. A good stability margin should then be obtained with a phase margin of 45° at the crossover frequency of 314 rad/s.

It is worthwhile mentioning that the transfer function Eq. (21) has double poles. It is classified as a Type-II system and capable of tracking a step phase or step frequency change with zero steady state error, although a constant phase error exists while it tracks a frequency ramp.

### 4. FREQUENCY VARIATION COMPENSATION

With the practical grid, power frequency may vary slightly from 50 Hz, potentially causing phase displacement and loss of magnitude in both tuned filters unequal to 45° and unity, respectively. Fig. 8(a) shows a phasor of the input voltage after being filtered by the phase-lead tuned filter. Its magnitude differs from that of the input voltage and a phase shift of 45° can no longer be achieved.

Fig. 9: Simulation block diagram using MATLAB/Simulink.

In order to correct the magnitude and phase, the error voltage phasor  $\Delta V_{\alpha}$  is added vectorially to the phasor of the phase-lead voltage  $V_{\alpha}$ . The compensated phase-lead voltage  $\widetilde{V_{\alpha}}$  can be expressed as

$$\widetilde{V_{\alpha}} = V_{\alpha} + \Delta V_{\alpha}. \tag{25}$$

Let the phase-lead voltage  $v_{\alpha}$  and the error voltage  $\Delta v_{\alpha}$  be expressed in the following sinusoidal functions:

$$v_{\alpha} = |V_{\alpha}| \sin(\omega_i t + \phi_{\alpha}) \tag{26}$$

$$\Delta v_{\alpha} = |\Delta V_{\alpha}| \sin(\omega_i t + \Delta \phi_{\alpha}) \tag{27}$$

$$\Delta v_{\alpha} = \operatorname{Re} \left\{ |\Delta V_{\alpha}| e^{j\Delta\phi_{\alpha}} \right\} \sin(\omega_{i}t) + \operatorname{Im} \left\{ |\Delta V_{\alpha}| e^{j\Delta\phi_{\alpha}} \right\} \cos(\omega_{i}t)$$

(28)

where  $\omega_i$  is an instantaneous value of the input frequency obtained from the phase detector. Their expressions for the real and imaginary parts are given as

$$\operatorname{Re}\left\{\left|\Delta V_{\alpha}\right| e^{j\Delta\phi_{\alpha}}\right\} = \left|V_{i}\right| \left(\frac{1}{\sqrt{2}} - \left|\frac{\omega_{i}k_{L\alpha}}{\left(\omega_{n\alpha}^{2} - \omega_{i}^{2}\right) + j\frac{\omega_{n\alpha}\omega_{i}}{Q_{\alpha}}}\right| \cos(\phi_{\alpha})\right)\right)$$

$$\operatorname{Im}\left\{\left|\Delta V_{\alpha}\right| e^{j\Delta\phi_{\alpha}}\right\} = \left|V_{i}\right| \left(\frac{1}{\sqrt{2}} - \left|\frac{\omega_{i}k_{L\alpha}}{\left(\omega_{n\alpha}^{2} - \omega_{i}^{2}\right) + j\frac{\omega_{n\alpha}\omega_{i}}{Q_{\alpha}}}\right| \sin(\phi_{\alpha})\right)$$

(29)

Fig. 8(b) shows a phasor of the phase-lag voltage. Its magnitude and phase need to be corrected in a similar manner to that previously mentioned. The compensated phase-lag voltage phasor  $\widetilde{V_\beta}$  can be expressed as

$$\widetilde{V_{\beta}} = V_{\beta} + \Delta V_{\beta} \tag{30}$$

$$\Delta v_{\beta} = \left| \Delta V_{\beta} \right| \sin \left( \omega_{i} t + \Delta \phi_{\beta} \right) \tag{31}$$

$$\Delta v_{\beta} = \operatorname{Re} \left\{ \left| \Delta V_{\beta} \right| e^{j\Delta\phi_{\beta}} \right\} \sin(\omega_{i}t) + \operatorname{Im} \left\{ \left| \Delta V_{\beta} \right| e^{j\Delta\phi_{\beta}} \right\} \cos(\omega_{i}t)$$

where  $\omega_i$  is the frequency value of the input voltage obtained from the phase detector. Their expressions for the real and imaginary parts are given as

$$\operatorname{Re}\left\{\left|\Delta V_{\beta}\right| e^{j\Delta\phi_{\beta}}\right\} = |V_{i}| \left(\frac{1}{\sqrt{2}} - \left|\frac{\omega_{i}k_{L\beta}}{\left(\omega_{n\beta}^{2} - \omega_{i}^{2}\right) + j\frac{\omega_{n\beta}\omega_{i}}{Q_{\beta}}}\right| \cos(\phi_{\beta})\right)$$

$$\operatorname{Im}\left\{\left|\Delta V_{\beta}\right| e^{j\Delta\phi_{\beta}}\right\} = \left|V_{i}\right| \left(\frac{1}{\sqrt{2}} - \left|\frac{\omega_{i}k_{L\beta}}{\left(\omega_{n\beta}^{2} - \omega_{i}^{2}\right) + j\frac{\omega_{n\beta}\omega_{i}}{Q_{\beta}}}\right| \sin(\phi_{\beta})\right)$$

(23)

The input voltage magnitude can be calculated as follows:

$$|V_i| = \sqrt{v_d^2 + v_q^2} = \sqrt{v_\alpha^2 + v_\beta^2}$$

(34)

In the event that the input voltage does not vary widely, its magnitude can be approximated by the nominal voltage.

## 5. SIMULATION RESULTS

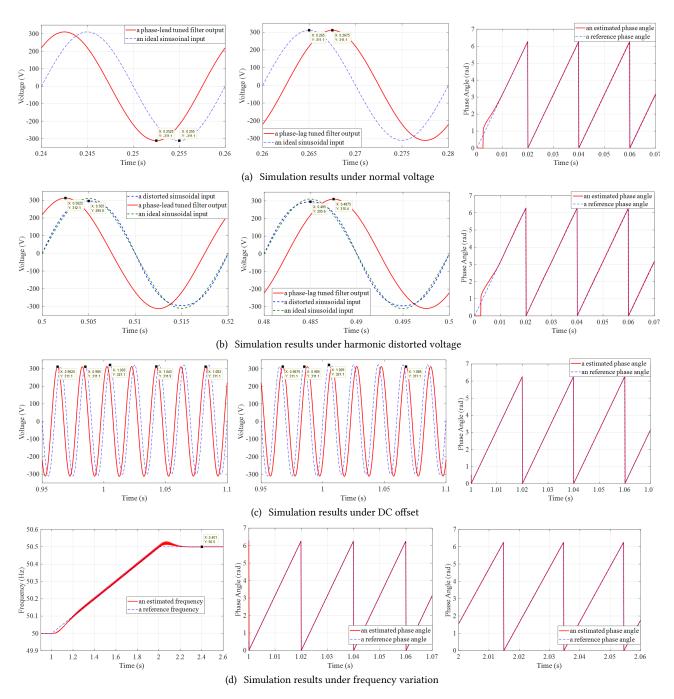

The feasibility of the proposed method is verified by computer simulation. Fig. 9 shows a block diagram implemented on MATLAB/Simulink. Six different voltage scenarios, i.e., normal, distorted harmonic, DC offset, frequency variation, phase jump, and frequency jump are simulated and the results illustrated.

Fig. 10(a) shows the waveforms of the voltages for the ideal grid, phase-lag, and phase-lead. The estimated phase angle catches up with the reference phase in less than half a period. Fig. 10(b) shows the distorted harmonic voltage, containing 5 percent of the third harmonic voltage. It is attenuated effectively by the phase-lead and phase-lag tuned filters while their magnitude and phase are correctly preserved. The method can precisely track

Fig. 10: Simulation results under four different voltage scenarios.

the phase of the grid. Fig. 10(c) shows waveforms of the grid voltage superimposed by 10 V DC offset at time 1.0 s. It disturbs the frequency slightly but has a noticeable effect on the estimated phase. Fig. 10(d) shows the grid voltage, the frequency of which changes slowly from 50 Hz to 50.5 Hz over a short period of time from 1 to 2 s. While frequency variation occurs, the proposed method can track the reference frequency, though there is a small magnitude of oscillation present on the estimated frequency. It does not cause any significant effect on the estimated phase because it is filtered out by the low bandwidth integrator. At the beginning of frequency variation at time 1.0 s, the phase of the grid voltage can be

estimated since it is essentially identical to the reference phase. After the frequency remains constant at 50.5 Hz, the estimated phase correctly tracks the reference phase.

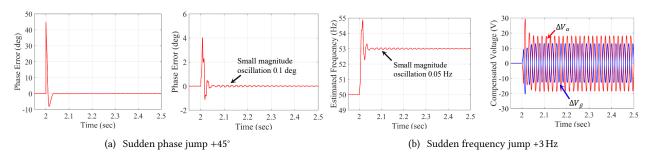

In Fig. 11(a), when a sudden phase jump of  $+45^\circ$  occurs, the phase error abruptly rises to  $+45^\circ$ , before rapidly returning to zero within two cycles with a small undershoot of  $6^\circ$ . Fig. 11(b) shows the response of the phase error and estimated frequency under a frequency jump of +3 Hz. The frequency variation compensation can correct the magnitude and phase of the phase-lead and phase-lag voltage. The zero phase error and accurate frequency estimation can be achieved within two cycles. A small magnitude of oscillation subsequently takes place

Fig. 11: Simulation results under (a) sudden phase and (b) frequency jumps.

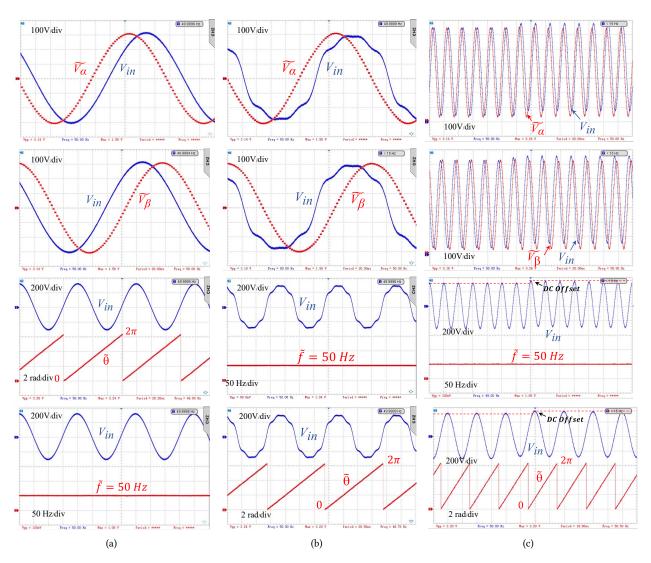

Fig. 12: Experimental results of voltage, estimated frequency, and phase angle under (a) normal voltage, (b) distorted harmonic voltage, and (c) voltage with DC offset.

on the estimated phase and frequency at a magnitude of  $0.1^{\circ}$  and  $0.05\,\mathrm{Hz}$ , respectively, but will decay to near zero in half a second.

## 6. EXPERIMENTAL RESULTS

The proposed method is implemented on a 32-bit microcontroller STM32F429ZIT6 and the algorithm executed repeatedly at  $4\,\mathrm{kHz}$ . The input voltage is sam-

pled via an ADC module and digitally filtered by the phase-lead and phase-lag tuned filters. Fig. 12(a) shows the triangular waveform phase of the grid voltage under normal voltage. At zero crossing, the phase counter is reset to zero. It then increases by 4.5 degrees with every step. Until the counter reaches 80, it is reset to zero and begins to count the phase for the next cycle. Fig. 12(b) shows a severely distorted waveform of the grid

voltage. It contains 10% of the third harmonic voltage, 7% of the fifth harmonic voltage, and 5% the seventh harmonic voltage. Despite the presence of harmonics, the method can detect the frequency and phase of the grid voltage correctly. The detected phase linearly increases and coincides with the fundamental component phase of the distorted grid voltage. Fig. 12(c) shows the grid voltage; superimposed instantly by the 10 V DC offset. Due to the nature of the capacitor in a series *RLC* circuit, the DC offset is blocked or quickly attenuated. Thus, the phase of the grid voltage can be detected precisely and seamlessly.

## 7. CONCLUSION

The phase lead-lag SRF-PLL is proposed in this paper to synchronize the grid of a single-phase inverter. The analysis and design example of the phase-lead and phase-lag tuned filters and phase detection algorithm have also been presented. The linearized model and controller design used to achieve good stability margin were discussed. The magnitude and phase compensation were detailed due to the frequency variation. Viability of the method was verified by the simulation based on MATLAB/Simulink platform. The algorithm was implemented on a 32-bit microcontroller and tested under various voltage conditions. According to the simulation and experimental results, it can be confirmed that the proposed method is robust and capable of accurately detecting the phase of the practical grid.

At the time of publication, the effect of the frequency variation compensation on the estimated quadraturephase voltage and control loop stability is being investigated and the analysis results will be presented in a future paper.

### REFERENCES

- [1] S. Sakamoto, T. Izumi, T. Yokoyama, and T. Haneyoshi, "A new method for digital PLL control using estimated quadrature two phase frequency detection," in *Proceedings of the Power Conversion Conference 2002*, pp. 671–676.

- [2] S. Golestan, J. M. Guerrero, A. Vidal, A. G. Yepes, J. Doval-Gandoy, and F. D. Freijedo, "Small-signal modeling, stability analysis and design optimization of single-phase delay-based PLLs," *IEEE Transac*tions on Power Electronics, vol. 31, no. 5, pp. 3517–3527, May 2016.

- [3] J.-W. Choi, Y.-K. Kim, and H.-G. Kim, "Digital PLL control for single-phase photovoltaic system," *IEE Proceedings Electric Power Applications*, vol. 153, no. 1, pp. 40–46, Jan. 2006.

- [4] Y. F. Wang and Y. W. Li, "Analysis and digital implementation of cascaded delayed-signal-cancellation PLL," *IEEE Transactions on Power Electronics*, vol. 26, no. 4, pp. 1067–1080, Apr. 2011.

- [5] Y. F. Wang and Y. W. Li, "Three-phase cascaded delayed signal cancellation PLL for fast selective

- harmonic detection," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 4, pp. 1452–1463, Apr. 2013.

- [6] L. Amuda, B. C. Filho, S. Silva, S. Silva, and A. Diniz, "Wide bandwidth single and three-phase PLL structures for grid-tied PV systems," in *Twenty-Eighth IEEE Photovoltaic Specialists Conference (IEEE-PESC* 2000), Anchorage, Alaska, USA, 2000, pp. 1660– 1663.

- [7] L. Hadjidemetriou, Y. Yang, E. Kyriakides, and F. Blaabjerg, "A synchronization scheme for singlephase grid-tied inverters under harmonic distortion and grid disturbances," *IEEE Transactions on Power Electronics*, vol. 32, no. 4, pp. 2784–2793, Apr. 2017.

- [8] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A new single-phase PLL structure based on second order generalized integrator," in 37th IEEE Power Electronics Specialists Conference, 2006, pp. 1511– 1516

- [9] M. Ciobotaru, R. Teodorescu, and V. G. Agelidis, "Offset rejection for PLL based synchronization in grid-connected converters," in 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, 2008, pp. 1611–1617.

- [10] M. Karimi-Ghartemani, S. A. Khajehoddin, P. K. Jain, A. Bakhshai, and M. Mojiri, "Addressing DC component in PLL and notch filter algorithms," *IEEE Transactions on Power Electronics*, vol. 27, no. 1, pp. 78–86, Jan. 2012.

- [11] J. Matas, M. Castilla, J. Miret, L. G. de Vicuna, and R. Guzman, "An adaptive prefiltering method to improve the speed/accuracy tradeoff of voltage sequence detection methods under adverse grid conditions," *IEEE Transactions on Industrial Electron*ics, vol. 61, no. 5, pp. 2139–2151, May 2014.

- [12] P. Rodriguez, A. Luna, I. Candela, R. Mujal, R. Teodorescu, and F. Blaabjerg, "Multiresonant frequency-locked loop for grid synchronization of power converters under distorted grid conditions," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 1, pp. 127–138, Jan. 2011.

- [13] X. Fang, Y. Wang, M. Li, and J. Liu, "A novel frequency-adaptive PLL for single-phase gridconnected converters," in 2010 IEEE Energy Conversion Congress and Exposition, 2010, pp. 414–419.

- [14] M. Karimi-Ghartemani and M. Iravani, "A method for synchronization of power electronic converters in polluted and variable-frequency environments," *IEEE Transactions on Power Systems*, vol. 19, no. 3, pp. 1263–1270, Aug. 2004.

- [15] M. Karimi-Ghartemani, B.-T. Ooi, and A. Bakhshai, "Application of enhanced phase-locked loop system to the computation of synchrophasors," *IEEE Transactions on Power Delivery*, vol. 26, no. 1, pp. 22–32, Jan. 2011.

- [16] L. Arruda, S. Silva, and B. Filho, "PLL structures for utility connected systems," in 2001 IEEE Industry Applications Conference. 36th IAS Annual Meeting, vol. 4, 2001, pp. 2655–2660.

[17] S. Preitl and R.-E. Precup, "On the algorithmic design of a class of control systems based on providing the symmetry of open-loop bode plots," Scientific Bulletin of the Politehnica University of Timisoara –Transactions on Automatic Control and Computer Science, vol. 41 (55), no. 2, pp. 47–55, Dec. 1996.

technology.

Thamvarit Singhavilai received his B.Eng. degree in Electrical Engineering from Mahidol University, Thailand, in 1998 and M.Eng. degree in Electrical Engineering from King Mongkut's Institute of Technology North Bangkok, Thailand, in 2002, and Ph.D. degree from University of Strathclyde, UK, in 2011. He is currently an Assistant Professor at the Department of Electrical Engineering, Mahidol University. His research interests are in electrical power system and railway

sources.

Chuttchaval Jeraputra received the B.Eng. degree in Electrical Engineering from King Mongkut's Institute of Technology, Ladkrabang, Thailand and the Ph.D. degree in Electrical Engineering from Texas A&M University College Station, TX in 2004. He is currently an assistant professor in the Department of Electrical Engineering, Mahidol University, Thailand. His research interests include power electronic converters and utility interface issues of renewable energy

Supun Tiptipakorn received the B.Eng. degree in Electrical Engineering from the King Mongkut's Institute of Technology Ladkrabang, Thailand; the Master of Business Administration (MBA), from the University of Toledo, Ohio, USA; the Master of Science in Electrical Engineering (MSEE) from the University of Wisconsin at Madison, Wisconsin, USA; and the Ph.D. degree in Electrical Engineering from the University of Texas at Arlington, Texas, USA. He worked at the

Electric Reliability Council of Texas (ERCOT), Texas, USA, as a Market Operations Support Specialist. Currently, he is the Chairman of the Electrical Engineering Department at the Mahidol University, Thailand. His research interests are the applications of system analysis and control techniques to power systems operation, protection, and planning.