# Minimal Realization Plus Current Output CC-based Biquad Circuit

Sompong Wisetphanichkij<sup>1†</sup>, Krit Angkeaw<sup>2</sup>, and Napat Sra-ium<sup>1</sup>, Non-members

### **ABSTRACT**

This paper presents a minimal design of a biquad circuit using only one plus current output type-II current conveyor (CCII), one differential voltage current conveyor (DVCC) and grounded passive components. The circuit enables the implementation of all 5 basic filter types: low-pass (LP), band-pass (BP), high-pass (HP), band-stop (BS) and all-pass (AP) by selecting and adding input and output currents with no component matching constraints. Moreover, the circuit parameters  $\omega_0$  and Q can be set simply by adjusting the circuit components. The proposed biquad circuit performance has very low sensitivity to circuit components due to its simple structure and a small number of devices (2 active and 4 grounded passive components). This allows the circuit to work at high frequencies. Non-ideal and parasitic effects are investigated and discussed. The performance of the proposed topology was evaluated through PSPICE simulator using the 0.18  $\mu$ m CMOS technology from the Taiwan Semiconductor Manufacturing Company (TSMC).

**Keywords**: Biquad Filter, Current Conveyors, Analog Signal Processing

#### 1. INTRODUCTION

Today, active circuits have been widely researched and used in a wide variety of applications. In particular, the high-performance characteristics current conveyor (CC) [1] circuits, such as reduced DC power supply requirements, reduced power consumptions, high precision, high current driving capability, high bandwidth, electronic tunability and high accuracy, are available. They have been developed to many variants such as Current Voltage Conveyor (CVC) [2], Inverting CCIIs [3], Differential-Voltage Current Conveyor [4], etc. With their efficiency, therefore, they are applied in various

Amplifier [6], Generalized Function Generator [7] or even Nonlinear Applications such as Precision Rectifiers [8], Multiplier/Divider [9]. High performance active filters have recently received much attention because current-mode filters have many

fields such as sinusoidal oscillator [5], Variable-gain

much attention because current-mode filters have many advantages compared with their voltage-mode counterpart [10-12]. The reason why current-mode circuits often performs differently from voltage-mode circuits is that current-mode circuits often use less loop gain and are less complex in terms of certain performance parameters such as propagation delay, dynamic range, and bandwidth. The characteristics of a current mode circuit make it not so vulnerable to the current demands of IC design trends, such as continuously decreased size, lower DC supply voltages and low power consumption [13-14]. Therefore, some active devices that could be exploited in both low voltage and low power have drawn a lot of attention, such as type-II current conveyor (CCII) [15], differential voltage current conveyor (DVCC) [16], differential difference current conveyor (DDCC) [17] and

For biquad filter, the name of this circuit was first used by J. Tow in 1968 [18] and later by L.C. Thomas in 1971 [19]. The name derives from the fact that the transfer function is a quadratic function in both the numerator and the denominator. Hence, the transfer function is a biquadratic function. Recently, there have been many alternative designs for biquad circuit [20-24]. A general class of current amplifier-based biquadratic filter circuits [20] uses the principle of adjacent networks to design a single-amplifier quadratic (SAB) filter circuit, however it requires several passive devices.

Fully differential current conveyor (FDCCII) has been used to design the biquad circuit [22, 25]. This device provides differential difference input voltages and differential output currents into a single circuit. The proposed circuit of [22] can realize all the five filter functions but it uses two capacitors along with 3 resistors. Although [25] has been improved to use fewer resistors, due to the complexity of the circuit resulting in the need for a large supply voltage for operation.

For tuneable biquad filter, a type of transconductance circuits is commonly used. [23] uses the current follower transconductance amplifier (CFTA) and [24] uses a voltage differencing transconductance amplifier (VDTA) to alter the filter properties. However, transconductance devices often have a limited operating range and easily cause a signal distortion. Tuneable current mode universal biquad filters have also been proposed by [21], using

Manuscript received on October 3, 2023; revised on February 10, 2024; accepted on February 12, 2024. This paper was recommended by Associate Editor Pipat Prommee.

<sup>&</sup>lt;sup>1</sup>The authors are with Department of Telecommunications Engineering, School of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL) Bangkok, Thailand.

<sup>&</sup>lt;sup>2</sup>The author is with Department of Instrumentation and Electronics Engineering King Mongkut's University of Technology North Bangkok (KMUTNB), Bangkok, Thailand.

<sup>&</sup>lt;sup>†</sup>Corresponding author: sompong.wi@kmitl.ac.th

<sup>© 2024</sup> Author(s). This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 4.0 License. To view a copy of this license visit: https://creativecommons.org/licenses/by-nc-nd/4.0/.

Digital Object Identifier: 10.37936/ecti-eec.2024222.251143

three active devices (multiple-output current conveyor, MOCC) and lots of passive devices.

For the VLSI implementation point of view, the simple structures and minimum number of active and passive components are important to reduce the power consumption, noise, space, and cost. The proposed current mode biquad circuit design uses two active devices, one plus current output type-II current conveyor (CCII+) [26-27] and one differential voltage current conveyor (DVCC) [4, 28]. The plus current output type-II current conveyor (CCII+) has a simpler circuit configuration than the minus current output circuit. Furthermore, it has a wide operating range and low power consumption compared to the minus current output current conveyor [26]. Both of them have a simple internal structure, which is able to operate at low voltages and retain low power consumption at high-speed operation. The proposed circuit requires 4 grounded passive components without requiring passive component matching constraints. It is very suitable for IC technology [29]. The circuit enables all 5 basic filter types, low-pass (LP), band-pass (BP), high-pass (HP), band-stop (BS) and all-pass (AP) implementing by selecting and adding the input and output currents with no component matching constraints. The circuit has the orthogonal adjusting capability for circuit parameters  $\omega_0$  and Q, which is required for an application. The proposed circuit use low supply voltage as  $\pm 0.6$ V which comparable to the circuit proposed by [30] using 1.2V differential difference transconductance amplifier as active device but less component count.

In the section 2 the active devices used in the designed filter are discussed. In the section 3 the block diagram and transfer functions of the proposed circuit are demonstrated. Section 4, the non-ideal analysis of these two active devices is used to see their impact on the operation of the circuit. Section 5, the parasitic effect of low-pass (LP) and band-pass (BP) is analysed. Next the simulation results of the proposed biquad circuit using PSPICE by using the 0.18 mm TSMC's CMOS technology are shown and then the conclusion.

# 2. PLUS CURRENT OUTPUT CURRENT CON-VEYOR (CCII+) AND DIFFERENTIAL VOLTAGE CURRENT CONVEYOR (DVCC)

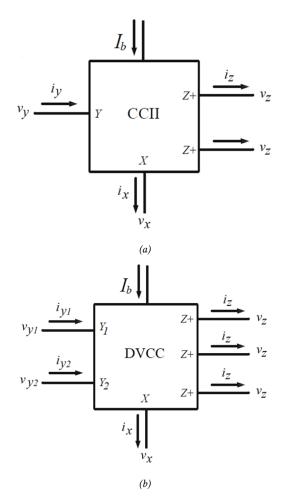

The dual plus current output second generation current conveyor (CCII+) and the multiple plus current output differential voltage current conveyor (DVCC) are symbolically shown in Fig. 1(a) and (b), respectively.

## 2.1 CCII+

A current conveyor is an abstraction for a threeterminal designated X, Y, and Z, an analogue electronic device. The potential at X equals whatever voltage is applied to Y and no current flows through terminal Y. As its name a current conveyor, any current out of terminal X is reflected at terminal Z. If the current flowing out of X resulted in the same direction of current flowing out of Z,

Fig. 1: (a) plus current output CCII+ [26] (b) plus current output DVCC [4,28].

it is called plus current output current conveyor circuit, CCII+. The CCII+ is characterized by

$$\begin{bmatrix} i_y \\ v_x \\ i_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_y \\ i_x \\ v_z \end{bmatrix}$$

(1)

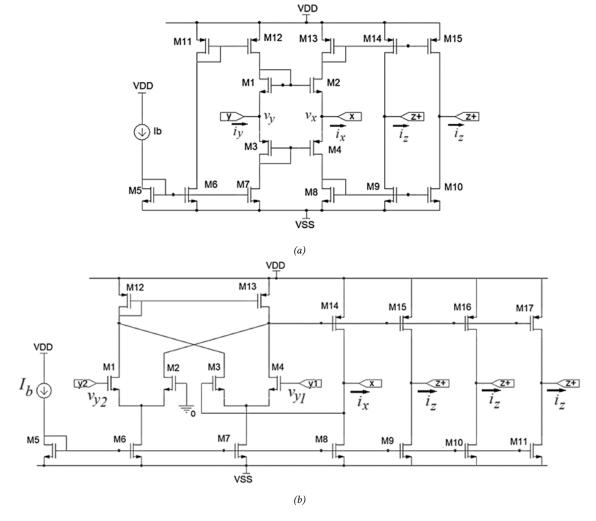

The current conveyor can be implemented in many forms. Fig. 2(a) shows CMOS CCII+ with Class AB configuration [27]. M1 to M4 act as Voltage followers which lead  $v_x$  equal to  $v_y$ . The bias current  $(I_b)$  sets the operating points of M1-M4 through current mirrors M6-M7 and M11-M12, which forces  $i_y$  equal to 0. The current mirrors (M8 to M10) and (M13 to M15) cause  $i_z$  equal to  $i_x$ .

### 2.2 **DVCC**

A differential voltage current conveyor (DVCC) [26] is a powerful analogue building block, especially for applications demanding differential or floating inputs like impedance converter circuits and current mode instrumentation amplifiers. It can be implemented by MOS transistor shown in Fig. 2(b). The DVCC is

Fig. 2: (a) plus current output CCII+ (b) plus current output DVCC [26].

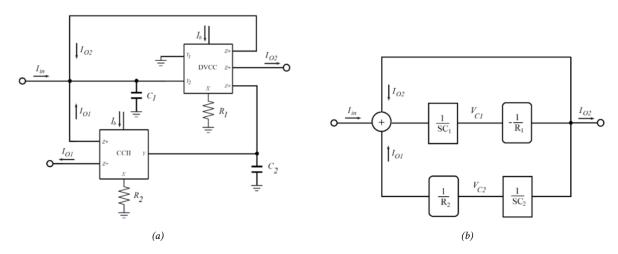

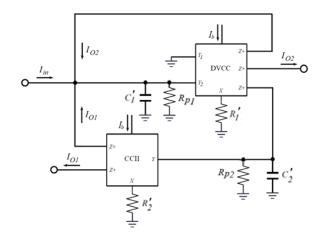

Fig. 3: (a) proposed circuit (b) equivalent block diagram.

(2)

characterized by

$$\begin{bmatrix} i_{y1} \\ i_{y2} \\ v_x \\ i_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_{y1} \\ v_{y2} \\ i_x \\ v_z \end{bmatrix}$$

The two differential stages composed of M1-M2 and M3- M4 and a current mirror M12-M13, which provide a relation of the  $v_x$  to be a differential voltage of  $v_{y1}$  and  $v_{y2}$ .

The M8 to M11 and M14 to M17 will duplicate  $i_x$  to

Fig. 4:  $R_1$  and  $R_2$  values when given  $C_1 = C_2 = 10 \ pF$ .

multiple  $i_z$  for using in the biquad circuit, which will be mentioned in the next section.

# 3. THE PROPOSED PLUS CURRENT OUTPUT CURRENT CONVEYOR BIQUAD CIRCUIT

The transfer function of biquad circuit is a quadratic function in both the numerator and the denominator, then T(s)

$$T(s) = \frac{a_2 S^2 + a_1 S + a_0}{S^2 + b_1 S + b_0}$$

$$= \frac{a_2 \left(S^2 + \left(\frac{\omega_Z}{Q_Z}\right) S + \omega_Z^2\right)}{S^2 + \left(\frac{\omega_P}{Q_P}\right) S + \omega_P^2}$$

(3)

Hence, the low-pass ( $a_2=a_1=0$ ), high-pass ( $a_1=a_0=0$ ), band-pass ( $a_2=a_0=0$ ), band-stop ( $a_1=0$ ) or all-pass responses can be performed. The proposed biquad circuit is comprised of one CCII+, one DVCC and 4 grounded components operating in current mode as shown in Fig. 3(a). Its equivalent circuit is shown in Fig. 3(b) that can be easily transformed into transfer functions:

$$T_{BP}(s) = \frac{I_{02}}{I_{in}}$$

$$= -\frac{sR_2C_2}{s^2R_1R_2C_1C_2 + sR_2C_2 + 1}$$

(4a)

$$T_{LP}(s) = \frac{I_{01}}{I_{in}}$$

$$= -\frac{1}{s^2 R_1 R_2 C_1 C_2 + s R_2 C_2 + 1}$$

(4b)

**Table 1**: Component Sensitivity.

| Component | ω0   | Q   |

|-----------|------|-----|

| $R_1$     | -0.5 | 0.5 |

| $R_2$     | -0.5 | 0.5 |

| $C_1$     | -0.5 | 0.5 |

| $C_2$     | -0.5 | 0.5 |

Therefore, a biquad filter parameter can be demonstrated as

$$\omega_0 = \sqrt{\frac{1}{R_1 R_2 C_1 C_2}}$$

(5a)

$$\frac{\omega_0}{Q} = \frac{1}{R_1 C_1} \tag{5b}$$

$$Q = \sqrt{\frac{R_1 C_1}{R_2 C_2}}$$

(5c)

Table 1 shows the sensitivity with respect to the circuit components.

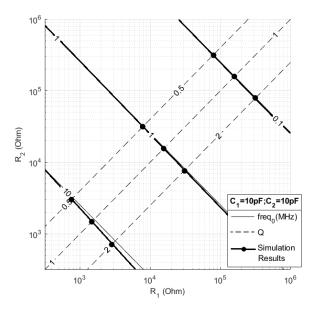

From (5a) and (5b), the parameters  $\omega_0$  and  $\omega_0/Q$  are orthogonally adjustable. For the fix-valued capacitors  $C_1$  and  $C_2$ , and the specified value of  $\omega_0$  and Q, the resistors  $R_1$  and  $R_2$  can be calculated as,

$$R_1 = \frac{Q}{C_1 \omega_0} \tag{6a}$$

$$R_2 = \frac{1}{C_2 \omega_0 Q} \tag{6b}$$

Although the parameters  $\omega_0$  and Q are interactive, the filter parameter control can be non-interactively obtained as follows: for the fix-valued capacitors,  $\omega_0$  can be tuned arbitrarily without disturbing Q while simultaneously changing  $R_1$  and  $R_2$  and keeping the ratio  $R_1/R_2$  constant. The parameter Q can also be adjusted without disturbing  $\omega_0$  by simultaneously changing  $R_1$  and  $R_2$  and keeping the product  $R_1R_2$  constant. The tunable grounded resistors can be used for  $R_1$  and  $R_2$  for electronically set the  $\omega_0$  and Q [31-33].

Fig. 4 shows examples of  $R_1$  and  $R_2$  values when  $f_0 = \omega_0/2\pi = 0.1$ , 1, 10, 100 MHz and when Q = 0.5, 1, and 2 when given  $C_1 = C_2 = 10 \mathrm{pF}$ .

The High-Pass (HP), Band-Stop (BS) and All-Pass (AP) filter can be achieved by the current manipulation by selection and addition of the circuit currents ( $I_{01}$  and  $I_{02}$ ) with the duplicated  $I_{in}$  which can be generated from a current copier circuit [34]. The corresponded circuit transfer functions are

$$T_{HP}(s) = \frac{I_{in}(s) + I_{01}(s) + I_{02}(s)}{I_{in}(s)}$$

$$= \frac{s^2 R_1 R_2 C_1 C_2}{s^2 R_1 R_2 C_1 C_2 + s R_2 C_2 + 1}$$

(7a)

$$T_{BS}(s) = \frac{I_{in}(s) + I_{02}(s)}{I_{in}(s)}$$

$$= \frac{s^2 R_1 R_2 C_1 C_2 + 1}{s^2 R_1 R_2 C_1 C_2 + s R_2 C_2 + 1}$$

(7b)

$$T_{AP}(s) = T_{BP}(s) + T_{BS}(s)$$

$$= \frac{s^2 R_1 R_2 C_1 C_2 - s R_2 C_2 + 1}{s^2 R_1 R_2 C_1 C_2 + s R_2 C_2 + 1}$$

(7c)

As shown in equations above, it can be deduced that all active and passive and sensitivities of this circuit are very low.

### 4. NON-IDEALITY ANALYSIS

In this section, we discuss the effect of non-idealities of the CCII+ and DVCC on the biquadratic characteristic. the DVCC non-idealities can be characterized by

$$\begin{bmatrix} i_{y1} \\ i_{y2} \\ v_x \\ i_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_{y1} \\ v_{y2} \\ i_x \\ v_z \end{bmatrix}$$

(8)

where  $R_{x1}$ ,  $a_1$  and  $b_{1i}$  (i = 1, 2) are intrinsic resistance at the x-terminal, current gain and voltage gain, respectively. As well as, The CCII+ considering the non-idealities is characterized by

$$\begin{bmatrix} i_y \\ v_x \\ i_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ \beta_2 & R_{x2} & 0 \\ 0 & \alpha_2 & 0 \end{bmatrix} \begin{bmatrix} v_y \\ i_x \\ v_z \end{bmatrix}$$

(9)

The current gains ( $a_i$ ; i = 1, 2) and voltage gains ( $b_i$ ; i = 1 and 2) can be expressed by using current-tracking error  $e_c \ll 1$  and voltage-tracking error  $e_{vi} \ll 1$  [28] as

$$\alpha_i = 1 - \varepsilon_{ci} \text{ and } \beta_i = 1 - \varepsilon_{vi}$$

(10)

Using equations (8) and (9), the biquad circuit transfer functions are derived under the conditions where  $a_1 = a_2 = a$  and  $b_{11} = b_{12} = b_2 = b$  as

$$T_{BP}(s) = \frac{I_{02}}{I_{in}}$$

$$= -\frac{\alpha \beta s R'_{2} C_{2}}{s^{2} R'_{1} R'_{2} C_{1} C_{2} + \alpha \beta s R'_{2} C_{2} + \alpha^{2} \beta^{2}}$$

(11a)

$$\begin{split} T_{LP}\left(s\right) &= \frac{I_{01}}{I_{in}} \\ &= -\frac{\alpha^{2}\beta^{2}}{s^{2}R'_{1}R'_{2}C_{1}C_{2} + \alpha\beta sR'_{2}C_{2} + \alpha^{2}\beta^{2}} \end{split} \tag{11b}$$

$$T_{HP}(s) = \frac{I_{in}(s) + I_{01}(s) + I_{02}(s)}{I_{in}(s)}$$

$$= \frac{s^2 R'_1 R'_2 C_1 C_2}{s^2 R'_1 R'_2 C_1 C_2 + \alpha \beta s R'_2 C_2 + \alpha^2 \beta^2}$$

(11c)

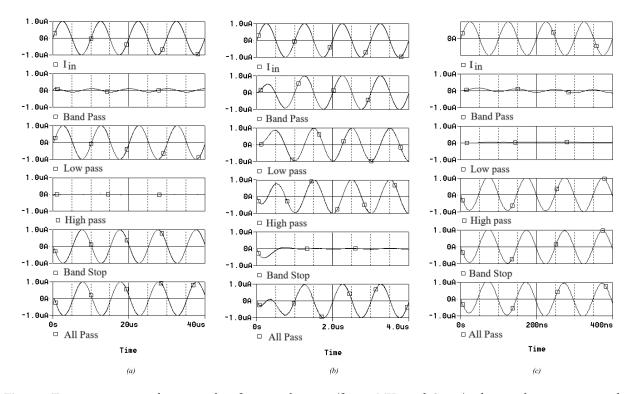

Fig. 5: Time responses simulation results of proposed circuit  $(f_0 = 1 MHz \text{ and } Q = 1)$  when apply input signal at frequency (a) 0.1 MHz, (b) 1 MHz and (c) 10 MHz.

$$T_{BS}(s) = \frac{I_{in}(s) + I_{02}(s)}{I_{in}(s)}$$

$$= \frac{s^2 R'_1 R'_2 C_1 C_2 + \alpha^2 \beta^2}{s^2 R'_1 R'_2 C_1 C_2 + \alpha \beta s R'_2 C_2 + \alpha^2 \beta^2}$$

(11d)

and.

$$T_{AP}(s) = T_{BP}(s) + T_{BS}(s)$$

$$= \frac{s^2 R_1 R_2 C_1 C_2 - s R_2 C_2 + 1}{s^2 R_1 R_2 C_1 C_2 + s R_2 C_2 + 1}$$

(11e)

where,

$$R'_1 = R_1 + R_{x1}$$

and  $R'_2 = R_2 + R_{x2}$  (12)

The circuit parameter  $\omega_0$  and Q become

$$\omega_0 = \frac{\alpha \beta}{\sqrt{R'_1 R'_2 C_1 C_2}} \tag{13}$$

$$Q = \sqrt{\frac{R'_1 C_1}{R'_2 C_2}} \tag{14}$$

Equations (13) and (14) demonstrate that deviations from ideal circuit characteristics arise due to non-ideal factors associated with the x-terminal resistance  $(R_x)$ , current gains  $(\alpha)$ , and voltage gains  $(\beta)$ . It is noteworthy that equation (13) reveals the potential for mitigating the influence of non-idealities on the circuit parameter  $\omega_o$  through the introduction of pre-distortion via the resistor  $R_i$ . Furthermore, the x-terminal resistances  $R_{x1}$  and  $R_{x2}$  can be precisely adjusted by manipulating the bias currents of the CCII+ and DVCC components. This underscores the significance of pre-tuning these bias currents as a viable means to effectively diminish the impact of non-idealities.

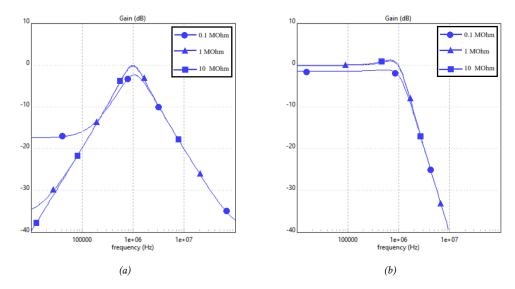

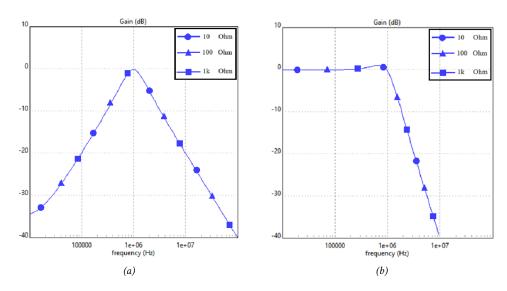

Fig. 6: Parasitic effect of parasitic resistance  $(R_{p1} = R_{p2})$  0.1, 1, and 10 MOhm (a) Band pass and (b) Low pass.

Fig. 7: Parasitic effect of parasitic resistance ( $R_{px1} = R_{px2}$ ) 10, 100, and 1 kOhm (a) Band pass and (b) Low pass.

### 5. PARASITIC EFFECT

Parasitic impedances of the proposed circuit are shown in Figure 5. The parasitic elements in components are in the internal circuit, the parasitic resistance of the component leads and the parasitic capacitance of the component packaging. The real DVCC and CCII have parasitic resistors and capacitors at terminal Y and Z to the ground and a serial resistor at the input terminal X. Considering the DVCC and CCII parasitic impedances, the transfer functions of the Low-pass and Band-pass the of proposed circuit are obtained and given in (15a) and (15b) for non-ideal case, respectively.

$R_{p1}$  is the parallel parasitic resistance of the input impedance of  $Y_2$  terminal of DVCC and the total effective output impedance of the two-output current mirrors of DVCC and CCII at Z+ terminal.

$R_{p2}$  is the parallel parasitic resistance of the the input impedance of Y terminal of CCII and the total effective

output impedance of the two-output current mirrors of DVCC at Z+ terminal.

$R'_1$  is the series resistance of  $R_1$  and the parasitic resistance of DVCC at X terminal  $(R_{px1})$ .

$R_2'$  is the series resistance of  $R_2$  and the parasitic resistance of CCII at X terminal  $(R_{p,x_2})$ .

$C_1'$  is the parallel capacitance of  $C_1$ , the input capacitance of  $Y_2$  terminal of DVCC and the total effective output capacitance of the two-output current mirrors of DVCC and CCII at Z+ terminal.

$C_2'$  is the parallel capacitance of  $C_2$ , the input capacitance of Y terminal of CCII and the total effective output capacitance of the two-output current mirrors of DVCC at terminal Z+.

At the X terminals parasitic series resistances decrease effective resistances, while at the Z and Y terminals parasitic parallel capacitances increase effective capacitances. In effects of parasitic impedance case, natural frequency

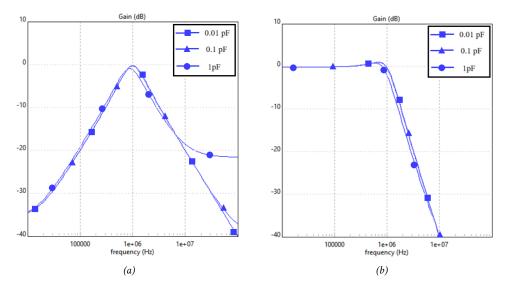

Fig. 8: Parasitic effect of parasitic capacitance for each terminal of DVCC and CCII 0.01, 0.1, and 1 pF (a) Band pass and (b) Low pass.

$$T_{LP}(s) = \frac{I_{01}}{I_{in}} = -\frac{1}{s^2 (C_1' C_2' R_1' R_2') + s \left( C_2' R_2' (1 + \frac{R_1'}{R_{p1}}) + C_1' R_1' R_2' \frac{1}{R_{p2}} \right) + (\frac{R_2'}{R_{p2}} + \frac{R_1' R_2'}{R_{p1} R_{p2}} + 1)}$$

(15a)

$$T_{BP}(s) = \frac{I_{02}}{I_{in}} = -\frac{s\left(C_2'R_2'\right) + \frac{R_2'}{R_{p2}}}{s^2(C_1'C_2'R_1'R_2') + s\left(C_2'R_2'(1 + \frac{R_1'}{R_{p1}}) + C_1'R_1'R_2'\frac{1}{R_{p2}}\right) + (\frac{R_2'}{R_{p2}} + \frac{R_1'R_2'}{R_{p1}} + 1)}$$

(15b)

$$\omega_0' = \left(\frac{1}{\sqrt{C_1'C_2'}}\right) \left(\sqrt{\frac{1}{R_1'R_2'} + \frac{1}{R_1'R_{p2}} + \frac{1}{R_{p1}R_{p2}}}\right)$$

(16a)

and,

$$Q' = \left(\frac{\sqrt{C_1'C_2'}}{\frac{C_1'}{R_{p2}} + C_2' \left(\frac{1}{R_1'} + \frac{1}{R_{p1}}\right)}\right) \left(\sqrt{\frac{1}{R_1'R_2'} + \frac{1}{R_1'R_{p2}} + \frac{1}{R_{p1}}R_{p2}}\right)$$

(16b)

$(\omega_0')$  and quality factor (Q') of the proposed circuit are found as (16).

From (16), it can be easily observed that the circuit parameter, the natural frequency ( $\omega_0'$ ) and quality factor (Q') changes depend on values of parasitic impedances. Fig. 6x-8x show the calculation results of the parasitic effect for the Band-pass (BP) and Low-Pass (LP). The nominal parasitic resistances ( $R_{p_1}$ ,  $R_{p_2}$ ), ( $R_{px1}$ ,  $R_{px2}$ ) and parasitic capacitance of each terminal are assumed to equal to 1 MOhm, 100 Ohm and 0.1pF, respectively. Fig. 6, 7 and 8 are calculation results of parasitic effect when alter ( $R_{p_1}$ ,  $R_{p_2}$ ), ( $R_{px1}$ ,  $R_{px2}$ ) and parasitic capacitances, respectively. The effect of parasitic resistance of DVCC and CCII at X terminal have less impact on circuit parameter ( $\omega_0'$  and Q') due to their small resistance when compare with  $R_1$  and  $R_2$ .

Table 2: Component Sensitivity.

| Mos transistors                     | W/L (µm) |  |  |

|-------------------------------------|----------|--|--|

| Plus current output CCII+ (Fig. 2a) |          |  |  |

| M1-M4                               | 15/0.18  |  |  |

| M5-M15                              | 5/0.35   |  |  |

| Plus current output DVCC (Fig. 2b)  |          |  |  |

| M1-M4                               | 15/0.18  |  |  |

| M5-M17                              | 5/0.35   |  |  |

### 6. SIMULATION RESULTS

The proposed circuit performance was evaluated through PSPICE simulator using the 0.18 ⊠m CMOS technology from Taiwan Semiconductor Manufacturing

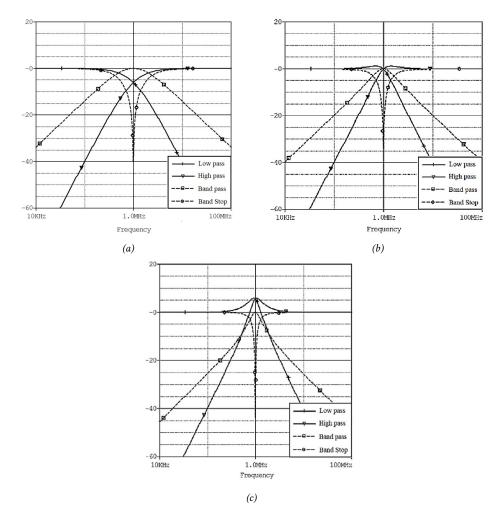

Fig. 9: Simulation results of proposed biquad circuit ( $f_0 = 1$ MHz) LP, HP, BP, BS (a) Q = 0.5, (b) Q = 1, (c) Q = 2.

**Table 3**: The set  $R_1$  and  $R_2$ .

| Q                                                           | 0.5   | 1      | 2     |  |  |

|-------------------------------------------------------------|-------|--------|-------|--|--|

| $R_1$                                                       | 7.96k | 15.92k | 31.8k |  |  |

| $R_2$                                                       | 31.8k | 15.92k | 7.96k |  |  |

| $(f_{\theta} = 1 \text{MHz and } C_1 = C_2 = 10 \text{pF})$ |       |        |       |  |  |

**Table 4**: Comparison with other current-mode biquad filter.

| Reference | No. of<br>active<br>component | No. of passive component | Supply<br>Voltage | All five-filter<br>function<br>realized |

|-----------|-------------------------------|--------------------------|-------------------|-----------------------------------------|

| [10]      | 2                             | 2                        | -                 | No                                      |

| [11]      | 4                             | 2                        | -                 | YES                                     |

| [16]      | 2                             | 5                        | ±1.5              | YES                                     |

| [21]      | 3                             | 3                        | ±1.5              | YES                                     |

| [22]      | 1                             | 5                        | $\pm 1.25$        | YES                                     |

| [23]      | 1                             | 3                        | ±3                | No                                      |

| [24]      | 1                             | 3                        | $\pm 1$           | YES                                     |

| [25]      | 1                             | 4                        | $\pm 1.65$        | YES                                     |

| [26]      | 3                             | 4                        | ±1.2              | YES                                     |

| [28]      | 2                             | 4                        | $\pm 1.5$         | YES                                     |

| [30]      | 5                             | 2                        | 1.2               | YES                                     |

| Proposed  | 2                             | 4                        | ±0.6              | YES                                     |

Company (TSMC). The aspect rations (W/L) of CCII+ and DVCC in Fig. 2 (a) and (b), respectively, are shown in table 2. DC supply is set to VDD = -VSS = 0.6V when bias current ( $I_b$ ) is set to 10  $\mu$ A.

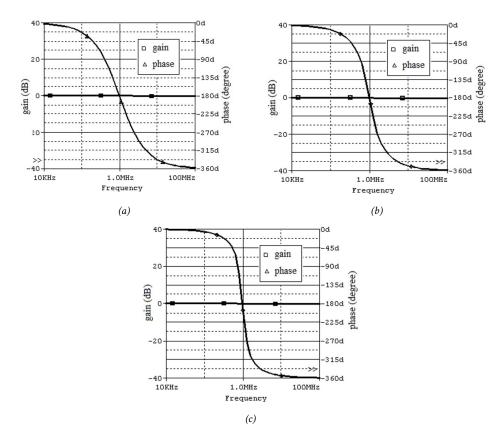

For simulating the filter circuit,  $I_{in}$  is set the amplitude to 1  $\mu$ A;  $f_0 = 1$  MHz. When given  $C_1 = C_2 = 10$  pF, equation (6) can be used to obtain  $R_1$  and  $R_2$  as shown in Table 3. The results of the simulation of Low-pass (LP), High-pass (HP), Band-pass (BP) and Band-stop (BS) filter are shown in Fig. 9 (a), (b) and (c) when Q = 0.5, 1 and 2, respectively. For All-pass (AP) filter, the simulation results are shown in Fig. 10 (a), (b) and (c) when Q = 0.5, 1 and 2. The power dissipation was 0.16 mW.

Fig. 11 is the time response simulation result of Lowpass (LP), High-pass (HP), Band-pass (BP), Band-stop (BS) and All-pass (AP) filter which is set to operate at  $f_0$  = 1MHz and Q = 1 by given  $C_1$  =  $C_2$  = 10pF and  $R_1$  =  $R_2$  = 15.92 kOhm. Fig. 11 (a), (b) and (c) is the time response when applied the input current signal at 0.1, 1 and 10 MHz, respectively.

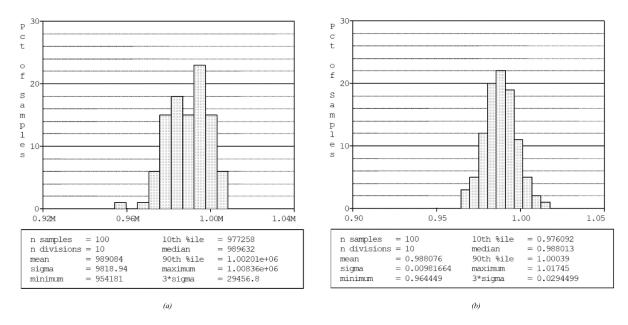

Furthermore, a Monte-Carlo analysis was conducted to assess the tolerance variations of passive components. The simulation involved subjecting the BP output to a Gaussian deviation of 1% in components  $C_1$ ,  $C_2$  (both set

Fig. 10: Simulation results of proposed biquad circuit ( $f_0 = 1$ MHz) AP (a) Q = 0.5, (b) Q = 1, (c) Q = 2.

**Fig. 11**: Time response simulation results of proposed circuit ( $f_0 = 1$  MHz and Q = 1) when applying input signal at frequency (a) 0.1MHz, (b) 1MHz and (c) 10MHz.

at 10pF), and R<sub>1</sub>, R<sub>2</sub> (both set at 15.92k $\Omega$ ), with the circuit configured for  $f_0=$  1MHz and Q= 1. This simulation

was executed iteratively in 100 runs. As depicted in Figures 12(a) and 12(b), the resulting histograms illustrate

**Fig. 12**: Monte-Carlo analysis results of proposed circuit (a)  $f_0$ , (b) Q.

the distributions of  $f_0$  and Q, respectively. These plots reveal that the simulated standard deviation and mean values for  $f_0$  are 9.818KHz and 0.989MHz, respectively, while for Q, they are 0.988 and 0.009, respectively. These findings indicate that variations in component values do not significantly impact the circuit's overall performance.

### 7. CONCLUSION

In this paper, a current mode biquad filter circuit is introduced. It composes of differential voltage current conveyor (DVCC) and the plus current output type-II current conveyor (CCII+), which have a simpler circuit configuration. Therefore, the circuit requires low supply voltage. The comparison with other current-mode biquad filter design is shown in Table 4. The proposed circuit offers several appealing characteristics, including the capability to realize all five essential functions, eliminating the need for component-matching requirements. It leverages the plus current output current conveyor approach to reduce power consumption and extend its suitability for wide-band applications. Additionally, the design utilizes all grounded passive components, making it highly suitable for integrated circuit (IC) implementation. Furthermore, the circuit provides orthogonal tunability for both  $\omega_0$  and Q parameters while demonstrating lowsensitivity performance. These advantageous attributes are substantiated by the simulation results and the outcomes of Monte-Carlo Analysis.

### **REFERENCES**

- [1] R. Senani, D.R. Bhaskar and A.K. Singh, Current Conveyors-Variants, Applications and Hardware Implementations, Springer, 2015.

- [2] I. M. Filanovsky and K. A. Stromsmoe, "Current-

- voltage conveyor," *Electronics Letters*, vol. 17, pp.129–130, 1981.

- [3] I. A. Awad IA and A. M. Soliman AM, "Inverting second generation current conveyors: the missing building blocks, CMOS realizations and applications," *International Journal of Electronics*, vol.86, pp. 413–432, 1999.

- [4] H. O. Elwan and A. M. Soliman, "Novel CMOS differential voltage current conveyor and its Applications," *IEE Proceedings - Circuits, Devices and Systems*, vol. 144, pp. 195–200, 1997.

- [5] R. Sotner, A. Lahiri, A. Kartci, N. Herencsar, J. Jerabek, K. Vrba, "Design of novel precise quadrature oscillators employing ECCIIs with electronic control," *Advances in Electrical and Computer Engineering*, vol. 13, pp. 65–72, 2013.

- [6] B. Wilson, "Constant bandwidth voltage amplification using current conveyors," *International Journal of Electronics*, vol. 65, pp. 983–988, 1988.

- [7] A. Sedra and K. C. Smith, "A second-generation current conveyor and its applications," *IEEE Transactions on Circuit Theory*, vol. 17, pp. 132–134, 1970.

- [8] C. Toumazou, F. J. Lidgey and S. Chattong, "High frequency current conveyor precision fullwave Rectifier," *Electronics Letters*, vol. 30, pp. 745–746, 1994.

- [9] S. Liu, D. S. Wu, H. W. Tsao, J. Wu and J. H. Tsay, "Nonlinear circuit applications with current Conveyors," *IEE Proceedings G (Circuits, Devices and Systems)*, vol. 140, 1993.

- [10] J. Ramirez-Angulo, M. Robinson and E. Sanchez-Sinecio, "Current-mode continuous-time filters: two design approaches," in *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 39, no. 6, pp. 337-341, June 1992.

- [11] T. Tsukutani, et al., "Current-mode biquad using OTAs and CF," *Electronics Letters*, vol.39, no.3, pp.262-263, 2003.

- [12] G. W. Roberts, A. S. Sedra, "All-current-mode frequency selective circuits," *Electronics Letters*, vol. 25, pp. 759-761, 1989.

- [13] H. Schmid, "Why the terms 'current mode' and 'voltage mode' neither divide nor qualify circuits," 2002 IEEE International Symposium on Circuits and Systems. Proceedings, Phoenix-Scottsdale, AZ, USA, 2002.

- [14] P. Woratraijariya, K. Mano, W. Jaikla and S. Maneewan, "Current-mode 4 quadrant divider employing only single active element," 2012 IEEE International Conference on Electron Devices and Solid State Circuit (EDSSC), Bangkok, Thailand, 2012, pp. 1-4.

- [15] G. Ferri and N. C. Guerrini, "Low-voltage low-power novel CCII topologies and applications," *ICECS 2001. 8th IEEE International Conference on Electronics, Circuits and Systems (Cat. No.01EX483)*, Malta, 2001, vol.2, pp. 1095-1098.

- [16] S. A. Mahmoud, "Low Voltage Wide Range CMOS Differential Voltage Current Conveyor and Its Applications," *Contemporary Engineering Sciences*, vol. 1, no. 3, , pp. 105-126, 2008.

- [17] F. Khateb, M. Kumngern, V. Spyridon, et al. "Differential Difference Current Conveyor Using Bulk-Driven Technique for Ultra-Low-Voltage Applications," *Circuits, Systems, and Signal Processing*, vol. 33, pp. 159–176, 2014.

- [18] J. Tow, "Active RC filters—A state-space realization," in *Proceedings of the IEEE*, vol. 56, no. 6, pp. 1137-1139, June 1968.

- [19] L. Thomas, "The Biquad: Part I-Some practical design considerations," in *IEEE Transactions on Circuit Theory*, vol. 18, no. 3, pp. 350-357, May 1971.

- [20] G. W. Roberts and A. S. Sedra, "A general class of current amplifier-based biquadratic filter circuits," in *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 39, no. 4, pp. 257-263, April 1992.

- [21] R. Senani, V. K. Singh and A. K. Singh, "Tunable currentmode universal biquads employing only three MOCCs and all grounded passive elements: Additional new realizations", *Frequenz*, vol. 59(9-10), pp. 220-224, 2005.

- [22] C. N. Lee and C. M. Chang, "Single FDCCII-Based Mixed-Mode Biquad Filter with Eight Outputs," AEU: International Journal of Electronics and Communications, vol. 63, no. 9, pp. 736-742, 2009.

- [23] W. Tangsrirat, "Novel Current-Mode and Voltage-Mode Universal Biquad Filters Using Single CFTA," *Indian Journal of Engineering and Material Science*, vol. 17, pp. 99-104, 2010.

- [24] D. Prasad, D. Bhaskar and M. Srivastava, "Universal Current-Mode Biquad Filter Using a VDTA," *Circuits and Systems*, vol. 4, no. 1, pp. 29-33, 2013.

- [25] T. Nonthaputha and M. Kumngern, "Current-mode universal filter using FDCCII," 2014 Twelfth International Conference on ICT and Knowledge Engineering, Bangkok, Thailand, 2014, pp. 32-35.

- [26] T. Tsukutani, N. Yabuki and K. Hashitsume, "Novel plus current output CC-based biquad circuit," 2021 36th International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC), 2021, pp. 1-4.

- [27] E. Brunn, "Class AB CMOS first –generation current conveyor," *Electronics Letters*, vol. 31, pp. 422–423, 1995.

- [28] Y. Sumi, T. Tsukutani and N. Yabuki, "Novel current-mode biquadratic circuit using only plus type DO-DVCCCs," 2008 International Symposium on Intelligent Signal Processing and Communications Systems, Bangkok, Thailand, 2009, pp. 1-4.

- [29] U. Çam, F. Kaçar, O. Cicekoglu, H. Kuntman, A. Kuntman, "Novel grounded parallel immittance simulator topologies employing single OTRA," AEU – International Journal of Electronics and Communications, vol. 57, pp. 287-290, 2003,

- [30] M. Kumngern, P. Suksaibul, F. Khateb and T. Kulej "1.2 V Differential Difference Transconductance Amplifier and Its Application in Mixed-Mode Universal Filter," Sensors, vol. 22, no. 9, p. 3535, 2022.

- [31] S. Wisetphanichkij, A. Binthawihok and K. Dejhan, "A new adjustable grounded/floating resistance circuit with enhanced dynamic range based on mixed-translinear loops," *IEEE International Sym*posium on Communications and Information Technology (ISCIT 2005), Beijing, China, 2005, pp. 267-270.

- [32] E. Yuce, S. Tokat and F. Yucel "A new wideband electronically tunable grounded resistor employing only three MOS transistors," *Turkish Journal of Electrical Engineering and Computer Sciences*, vol. 24, pp. 2442–2453, 2015.

- [33] A. Chhabra, R. Senani, Raj and B. Aggarwal, "Wide-range current-controlled grounded resistor realization: A new application of the CMOS translinear elements," *International Journal of Cir*cuit Theory and Applications, vol. 51, pp. 3622-3636, 2003.

- [34] R. Huang and C. Wey, "Design of high-speed high-accuracy current copiers for low-voltage analog signal processing applications," in *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 43, no. 12, pp. 836-839, Dec. 1996.

Sompong Wisetphanichkij received the M.Eng. and D.Eng. degrees in electrical engineering from the Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand, in 1998 and 2008, respectively. Since 2002, he has been a Faculty Member with the King Mongkut's Institute of Technology Ladkrabang (KMITL), where he is currently an Assistant Professor with the Department of

Telecommunications Engineering. His research interests are focusing in analog signal processing, analog filter design and CMOS analog integrated circuit design.

Krit Angkeaw received the B.Ind.Tech. degree in electronics engineering from Siam University, Bangkok, Thailand, in 1996, and the M.Eng. and D.Eng. degrees in electrical engineering from the Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand, in 2000 and 2009, respectively. Since 2004, he has been a Faculty Member with the King Mongkut's University of Technology North Bangkok (KMUTNB), where he is currently an Associate Professor with the Instrumentation and Electronics

Engineering Department. His research interests are focusing in analog filter, interface circuit for sensors, and electronic instrumentation.

Napat Sra-ium received the M.Eng. and D.Eng. degrees in electrical engineering from D.Eng. degrees in electrical engineering from the Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand, in 1998 and 2012, respec-tively. Since 1994, he has been a Faculty Member with the King Mongkut's Institute of Technology Ladkrabang (KMITL), where he is currently an Assistant Professor with the Department of Telecommunications Engineering. His research interests are focusing in

networking, cyber security and data analytics.